EK-KDJ1A-UG-002

# KDJ11-A CPU Module User's Guide

# KDJ11-A CPU Module User's Guide

Prepared by Educational Services of Digital Equipment Corporation

Preliminary Edition, January 1984 1st Edition, May 1984 2nd Edition, June 1986

© Digital Equipment Corporation 1986. All Rights Reserved. Printed in U.S.A.

The material in this manual is for informational purposes and is subject to change without notice. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this manual.

The manuscript for this book was created on a VAX-11/780 system and, via a translation program, was automatically typeset by Digital's DECset Integrated Publishing System. The book was produced by Educational Services Development and Publishing in Marlboro, MA.

The following are trademarks of Digital Equipment Corporation:

| digital      | MicroPower/Pascal | RSX            |

|--------------|-------------------|----------------|

| DEC          | MINC-11           | RT             |

| DECmate      | OMNIBUS           | RT-11          |

| DECnet       | OS/8              | TOPS-10        |

| DECsystem-10 | PDP               | TOPS-20        |

| DECSYSTEM-20 | PDT               | UNIBUS         |

| DECUS        | P/OS              | VAX            |

| DECwriter    | Professional      | VAXstation     |

| DIBOL        | Q-Bus             | VAXstation II  |

| EduSystem    | Q22-Bus           | VMS            |

| IAS          | Rainbow           | VT             |

| MASSBUS      | RSTS              | Work Processor |

# **CONTENTS**

# Page

# CHAPTER 1 ARCHITECTURE

| 1.1     | DESCRIPTION                                              | 1-1  |

|---------|----------------------------------------------------------|------|

| 1.2     | GENERAL PURPOSE REGISTERS                                |      |

| 1.2.1   | Registers                                                | 1-2  |

| 1.2.2   | Stack Pointer                                            |      |

| 1.2.3   | Program Counter                                          | 1-3  |

| 1.3     | SYSTEM CONTROL REGISTERS                                 | 1-3  |

| 1.3.1   | Processor Status Word (Address: 17 777 776)              | 1-3  |

| 1.3.2   | CPU Error Register (Address: 17 777 766)                 |      |

| 1.3.3   | Program Interrupt Request Register (Address: 17 777 772) | 1-6  |

| 1.3.4   | Line Time Clock Register (Address: 17 777 546)           | 1-7  |

| 1.3.5   | Maintenance Register (Address: 17 777 750)               |      |

| 1.4     | INTERRUPTS                                               | 1-8  |

| 1.5     | MEMORY MANAGEMENT                                        | 1-10 |

| 1.5.1   | Memory Mapping                                           | 1-10 |

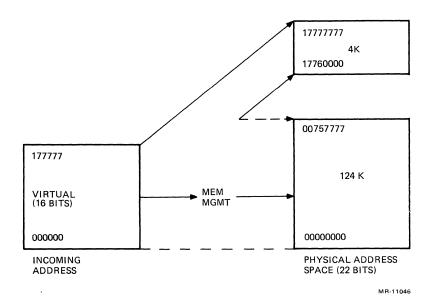

| 1.5.1.1 | 16-Bit Mapping                                           | 1-11 |

| 1.5.1.2 | 18-Bit Mapping                                           | 1-11 |

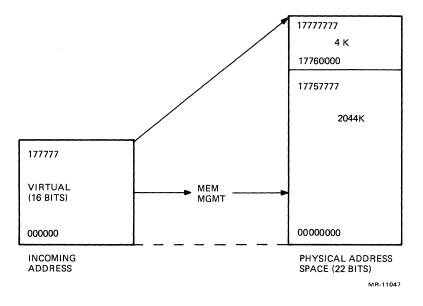

| 1.5.1.3 | 22-Bit Mapping                                           | 1-12 |

| 1.5.2   | Compatibility                                            | 1-12 |

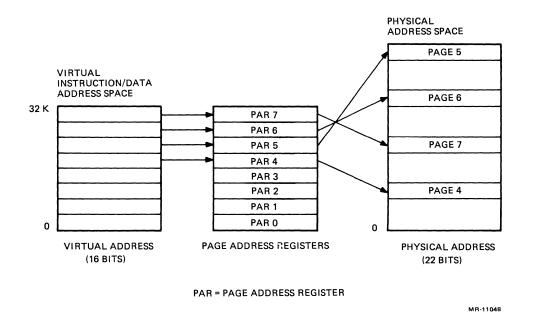

| 1.5.3   | Virtual Addressing                                       | 1-13 |

| 1.5.4   | Interrupt Conditions Under Memory Management Control     | 1-13 |

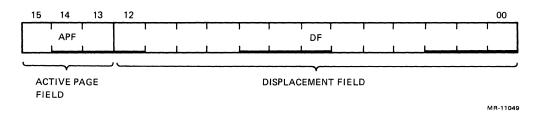

| 1.5.5   | Construction of a Physical Address                       | 1-14 |

| 1.5.6   | Memory Management Registers                              | 1-16 |

| 1.5.6.1 | Page Address Registers                                   | 1-18 |

| 1.5.6.2 | Page Descriptor Register                                 |      |

| 1.5.7   | Fault Recovery Registers                                 | 1-18 |

| 1.5.7.1 | Memory Management Register 0 (Address: 17 777 572)       | 1-20 |

| 1.5.7.2 | Memory Management Register 1 (Address: 17 777 574)       | 1-21 |

| 1.5.7.3 | Memory Management Register 2 (Address: 17 777 576)       | 1-21 |

| 1.5.7.4 | Memory Management Register 3 (Address: 17 772 516)       | 1-21 |

| 1.5.7.5 | Instruction Back-Up/Restart Recovery                     | 1-22 |

| 1.5.7.6 | Clearing Status Registers Following Abort                | 1-22 |

| 1.5.7.7 | Multiple Faults                                          | 1-22 |

| 1.5.8   | Typical Usage Examples                                   | 1-22 |

| 1.5.8.1 | Typical Memory Page                                      | 1-23 |

| 1.5.8.2 | Nonconsecutive Memory Pages                              | 1-25 |

| 1.5.8.3 | Stack Memory Pages                                       |      |

| 1.5.9   | Transparency                                             | 1-27 |

## Page

| 1.6       | CACHE MEMORY                                       | 1-27       |

|-----------|----------------------------------------------------|------------|

| 1.6.1     | Parity                                             | 1-29       |

| 1.6.1.1   | Parity Errors                                      |            |

| 1.6.1.2   | Multiple Cache Parity Errors                       |            |

| 1.6.2     | Memory System Registers                            |            |

| 1.6.2.1   | Cache Control Register (Address: 17 777 746)       | 1-30       |

| 1.6.2.2   | Hit/Miss Register (Address: 17 777 752)            |            |

| 1.6.2.3   | Memory System Error Register (Address: 17 777 744) | 1-32       |

| 1.7       | SOFTWARE SYSTEMS                                   | 1-33       |

| 1.7       | SOI I WARE STOTEND                                 | 1 55       |

| CHAPTER 2 | INSTALLATION                                       |            |

| 2.1       | INTRODUCTION                                       | 2-1        |

| 2.2       | CONFIGURATION                                      | 2-1        |

| 2.2.1     | Power-Up Options                                   |            |

| 2.2.1.1   | Power-Up Option 0                                  |            |

| 2.2.1.2   | Power-Up Option 1                                  |            |

| 2.2.1.3   | Power-Up Option 2                                  |            |

| 2.2.1.4   | Power-Up Option 3                                  |            |

| 2.2.2     | HALT Option.                                       |            |

| 2.2.2     | Boot Address                                       |            |

| 2.2.4     | Wakeup Disable                                     |            |

| 2.2.5     | BEVNT Recognition                                  |            |

| 2.2.5     | Factory Configuration                              |            |

| 2.2.0     | DIAGNOSTIC LEDS                                    |            |

| 2.3       | MAINTENANCE REGISTER (ADDRESS 17 777 750)          | ······ 2-4 |

| 2.4 2.5   | MAINTENANCE REUISTER (ADDRESS 1/ /// /30)          |            |

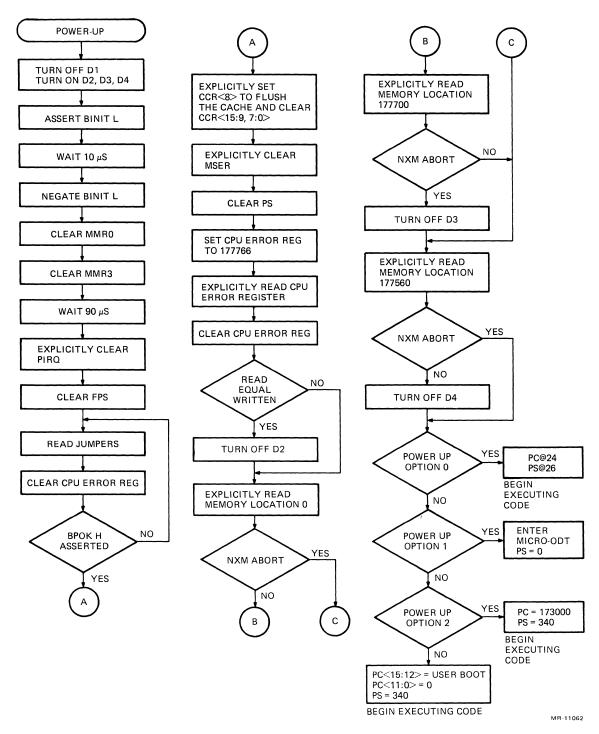

|           | POWER-UP SEQUENCE                                  |            |

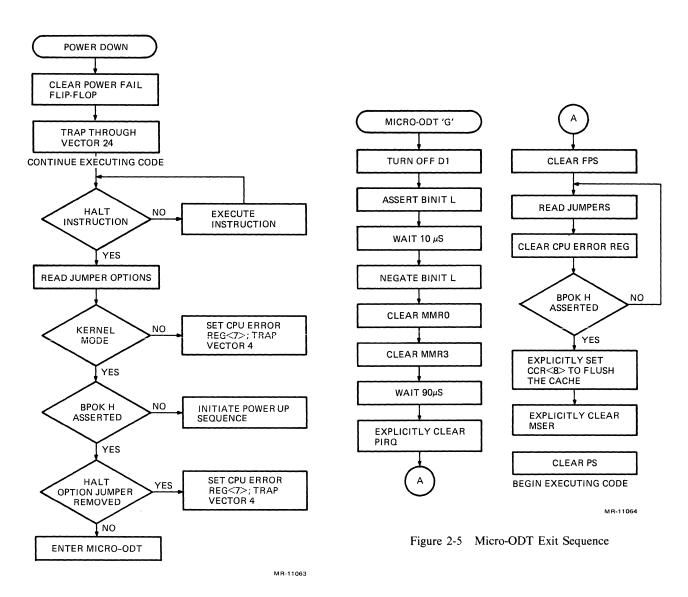

| 2.6       | POWER-DOWN SEQUENCE                                |            |

| 2.7       | EXIT MICRO-ODT SEQUENCE                            |            |

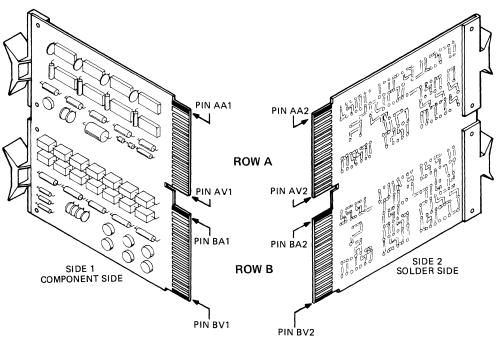

| 2.8       | MODULE CONTACT FINGER IDENTIFICATION               |            |

| 2.9       | HARDWARE OPTIONS                                   |            |

| 2.9.1     | LSI-11 Options                                     |            |

| 2.9.2     | Restricted LSI-11 Options                          |            |

| 2.9.3     | Enclosures                                         | 2-14       |

| 2.10      | SYSTEM DIFFERENCES                                 |            |

| 2.11      | KDJ11-A SYSTEM                                     | 2-16       |

| 2.12      | MODULE INSTALLATION PROCEDURE                      |            |

| 2.13      | SPECIFICATIONS                                     | 2-18       |

| CHAPTER 3 | CONSOLE ON-LINE DEBUGGING TECHNIQUE (ODT)          |            |

| 3.1       | INTRODUCTION                                       | 3-1        |

| 3.2       | TERMINAL INTERFACE                                 | 3-1        |

| 3.3       | CONSOLE ODT ENTRY CONDITIONS                       |            |

| 3.4       | ODT OPERATION OF THE CONSOLE SERIAL-LINE INTERFACE |            |

| 3.4.1     | Console ODT Input Sequence                         | 3-3        |

| 3.4.2     | Console ODT Output Sequence                        | 3-3        |

| 3.5       | CONSOLE ODT COMMAND SET                            | 3-3        |

| 3.5.1     | /(ASCII 057) – Slash                               |            |

3.5.2

# Page

| 3.5.3 | <lf> (ASCII 12) – Line Feed</lf>                               |     |

|-------|----------------------------------------------------------------|-----|

| 3.5.4 | \$ (ASCII 044) or R (ASCII 122) – Internal Register Designator |     |

| 3.5.5 | S (ASCII 123) – Processor Status Word Designator               |     |

| 3.5.6 | G (ASCII 107) – Go                                             |     |

| 3.5.7 | P (ASCII 120) – Proceed                                        | 3-7 |

| 3.5.8 | Control-Shift-S (ASCII 23) – Binary Dump                       | 3-7 |

| 3.6   | KDJ11-A ADDRESS SPECIFICATION                                  | 3-8 |

| 3.6.1 | Processor I/O Addresses                                        | 3-8 |

| 3.6.2 | Stack Pointer Selection                                        | 3-8 |

| 3.6.3 | Entering of Octal Digits                                       | 3-8 |

| 3.6.4 | ODT Timeout                                                    | 3-9 |

| 3.7   | INVALID CHARACTERS                                             | 3-9 |

# CHAPTER 4 FUNCTIONAL THEORY

| 4.1      | INTRODUCTION                        |      |

|----------|-------------------------------------|------|

| 4.2      | DCJ11 MICROPROCESSOR                | 4-3  |

| 4.2.1    | Initialization (MINIT L)            | 4-3  |

| 4.2.2    | Output Signals                      | 4-3  |

| 4.2.2.1  | Address Input/Output (AIO<03:00> H) | 4-3  |

| 4.2.2.2  | Bank Select, (BS1 H, BS0 H)         | 4-4  |

| 4.2.2.3  | Address Latch Enable (ALE L)        | 4-5  |

| 4.2.2.4  | Stretch Control (SCTL L)            | 4-5  |

| 4.2.2.5  | Strobe (STRB L)                     | 4-5  |

| 4.2.2.6  | Buffer Control (BUFCTL L)           | 4-5  |

| 4.2.2.7  | Predecode Strobe (PRDC L)           | 4-5  |

| 4.2.2.8  | Clock (CLK H)                       | 4-5  |

| 4.2.3    | Input Signals                       | 4-5  |

| 4.2.3.1  | MISS L                              | 4-5  |

| 4.2.3.2  | Data Valid (DV'L)                   | 4-5  |

| 4.2.3.3  | Continue (CONT L)                   | 4-5  |

| 4.2.3.4  | DMA Request (DMR L)                 |      |

| 4.2.3.5  | IRQ <07:04> H                       | 4-5  |

| 4.2.3.6  | HALT H                              | 4-5  |

| 4.2.3.7  | EVNT H                              | 4-6  |

| 4.2.3.8  | PWR FAIL L                          | 4-6  |

| 4.2.3.9  | PARITY L                            | 4-6  |

| 4.2.3.10 | ABORT L                             | 4-6  |

| 4.2.3.11 | FPA FPE L                           | 4-6  |

| 4.2.4    | MDAL <21:00>                        |      |

| 4.2.5    | DCJ11 Timing                        | 4-6  |

| 4.2.5.1  | NOP                                 | 4-6  |

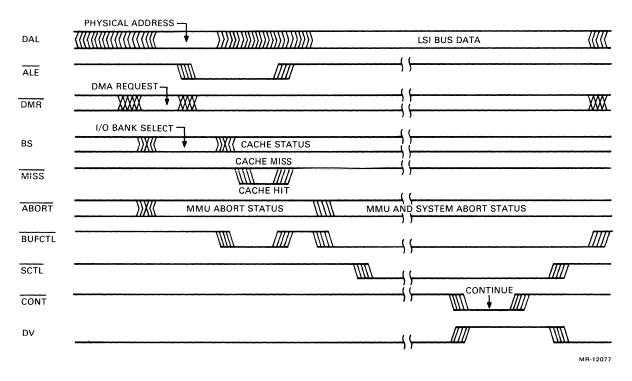

| 4.2.5.2  | Bus Read                            | 4-7  |

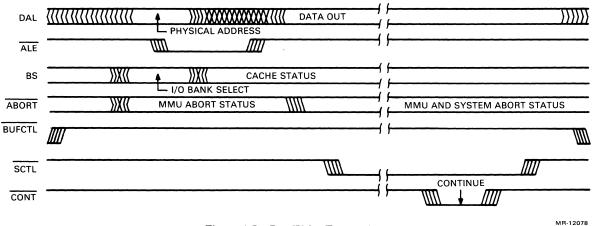

| 4.2.5.3  | Bus Write                           | 4-8  |

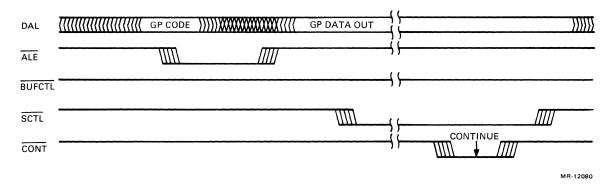

| 4.2.5.4  | General-Purpose Read                | 4-9  |

| 4.2.5.5  | General-Purpose Write               | 4-10 |

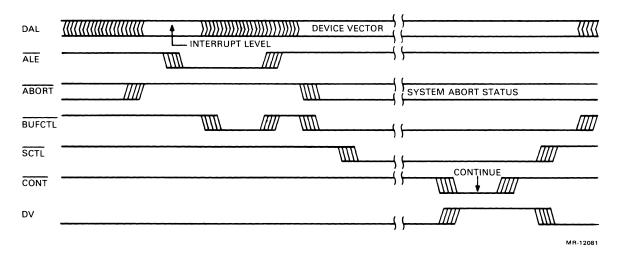

| 4.2.5.6  | IACK                                |      |

| 4.3      | STATE SEQUENCER                     | 4-10 |

| 4.3.1    | DCJ11                               |      |

| 4.3.2    | LSI-11 Bus Signals                  | 4-12 |

|          |                                     |      |

# Page

| 4.3.3     | LSI-11 Bus Receivers                | 4-12 |

|-----------|-------------------------------------|------|

| 4.3.4     | LSI-11 Bus Transmitters             |      |

| 4.3.5     | Maintenance Register                |      |

| 4.3.6     | DMA Register                        |      |

| 4.3.7     | Cache Data Path                     |      |

| 4.3.8     | Cache Memory                        |      |

| 4.3.9     | Floating-Point Accelerator          |      |

| 4.3.10    | Bus Traffic                         |      |

| 4.3.10.1  | Address Busing                      |      |

| 4.3.10.2  | Read Data                           |      |

| 4.3.10.3  | Write Data                          |      |

| 4.4       | CACHE DATA PATH                     |      |

| 4.4.1     | DCJ11 Input Signals                 |      |

| 4.4.2     | State Sequencer Inputs              |      |

| 4.4.3     | System Memory Parity                |      |

| 4.4.4     | Cache Memory Parity                 |      |

| 4.4.5     | Timeout                             |      |

| 4.4.6     | Cache Control Register              |      |

| 4.4.7     | Memory System Error Register        |      |

| 4.4.8     | LTC Register                        |      |

| 4.4.9     | Flush Counter                       |      |

| 4.4.10    |                                     |      |

| 4.4.11    | Address Register                    |      |

| 4.4.11    | CDP Outputs<br>CACHE MEMORY         |      |

| 4.5.1     |                                     |      |

| 4.5.2     | Cache Data                          |      |

|           | Data Parity Logic                   |      |

| 4.5.3     | Parity Data                         |      |

| 4.5.4     | TAG RAM                             |      |

| 4.5.5     | Hit/Miss Logic                      |      |

| 4.6       | BUS RECEIVERS                       |      |

| 4.7       | BUS TRANSMITTERS                    |      |

| 4.8       | OUTPUT CONTROL                      |      |

| 4.9       | INPUT CONTROL                       |      |

| 4.10      | DMA MONITOR REGISTER                |      |

| 4.11      | INITIALIZATION/MAINTENANCE REGISTER |      |

| 4.12      | STATUS LEDs                         | 4-29 |

| CHAPTER 5 | EXTENDED LSI-11 BUS                 |      |

| 5.1       | INTRODUCTION                        |      |

| 5.2       | BUS SIGNAL NOMENCLATURE             |      |

| 5.3       | DATA TRANSFER BUS CYCLES            |      |

| 5.3.1     | Bus Cycle Protocol                  |      |

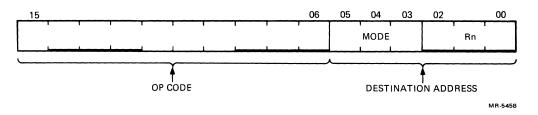

| 5.3.1.1   | Device Addressing                   | 5-4  |

| 5.3.1.2   | DATI                                |      |

| 5.3.1.3   | DATO(B)                             |      |

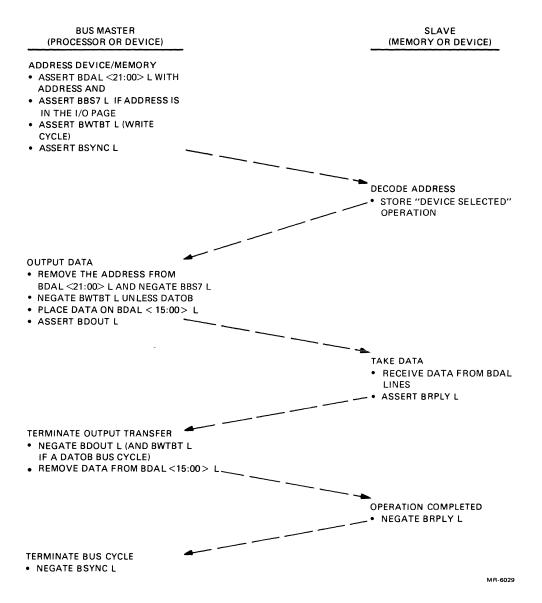

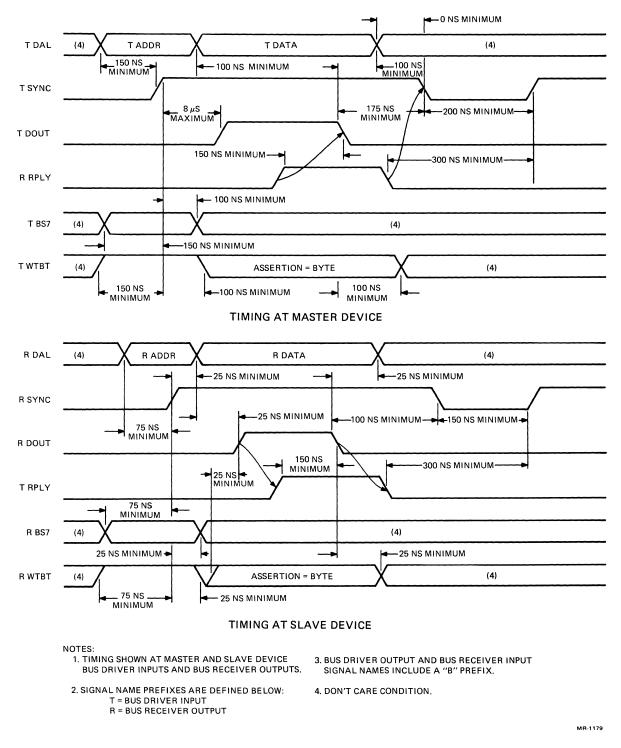

| 5.3.1.4   | DATIO(B)                            |      |

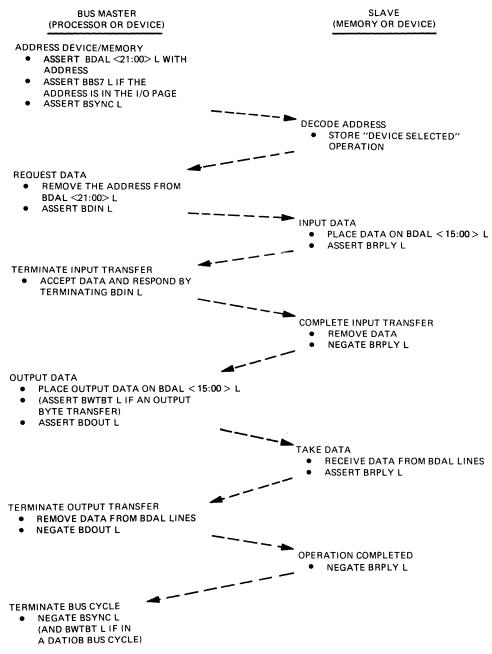

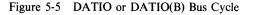

| 5.3.1.5   | DATIO(B)                            |      |

| 5.3.1.6   | DATBI                               |      |

| 2.2.1.0   |                                     |      |

5.4

# Page

|           |                                                                 | c 1 C |

|-----------|-----------------------------------------------------------------|-------|

| 5.5       | INTERRUPTS                                                      |       |

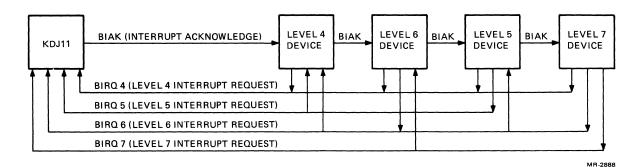

| 5.5.1     | Device Priority                                                 | 5-17  |

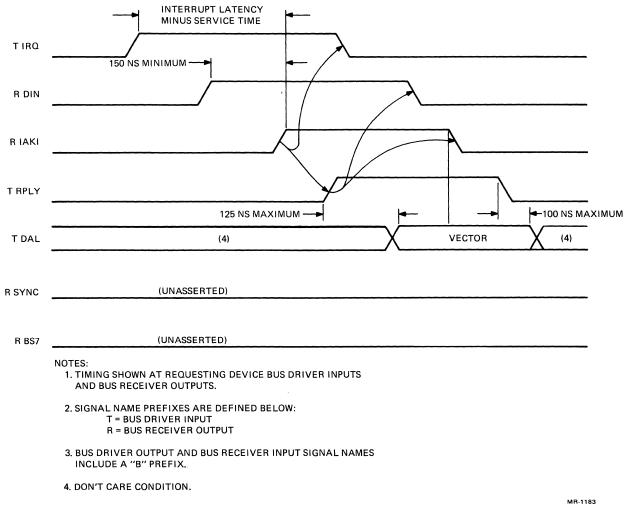

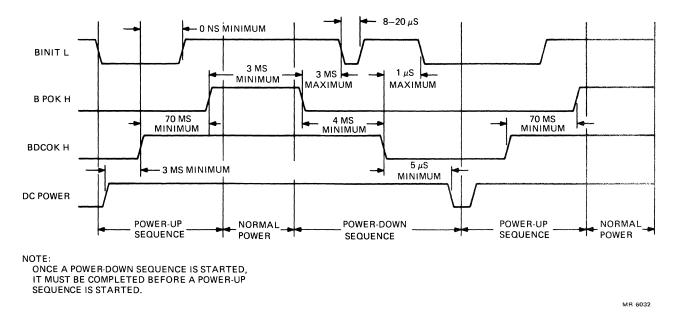

| 5.5.2     | Interrupt Protocol                                              | 5-18  |

| 5.5.3     | 4-Level Interrupt Configurations                                | 5-21  |

| 5.6       | CONTROL FUNCTIONS                                               | 5-22  |

| 5.6.1     | Memory Refresh                                                  |       |

| 5.6.2     | Halt                                                            |       |

| 5.6.3     | Initialization                                                  |       |

|           |                                                                 |       |

| 5.6.4     | Power Status                                                    |       |

| 5.6.4.1   | BDCOK H                                                         |       |

| 5.6.4.2   | BPOK H                                                          |       |

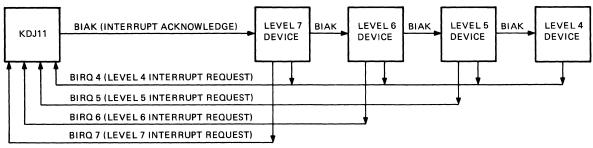

| 5.6.4.3   | Power-Up                                                        | 5-23  |

| 5.6.4.4   | Power-Down                                                      | 5-24  |

| 5.6.5     | BEVNT L                                                         | 5-24  |

| 5.7       | BUS ELECTRICAL CHARACTERISTICS.                                 |       |

| 5.7.1     | Signal-Level Specification                                      |       |

| 5.7.2     | AC Bus Load Definition                                          |       |

|           |                                                                 |       |

| 5.7.3     | DC Bus Load Definition                                          |       |

| 5.7.4     | 120 $\Omega$ LSI-11 Bus                                         |       |

| 5.7.5     | Bus Drivers                                                     |       |

| 5.7.6     | Bus Receivers                                                   | 5-26  |

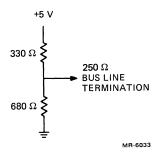

| 5.7.7     | KDJ11-A Bus Termination                                         | 5-26  |

| 5.7.8     | Bus Interconnection Wiring                                      |       |

| 5.7.8.1   | Backplane Wiring                                                |       |

| 5.7.8.2   | Intrabackplane Bus Wiring                                       |       |

|           |                                                                 |       |

| 5.7.8.3   | Power and Ground                                                |       |

| 5.7.8.4   | Maintenance and Spare Pins                                      |       |

| 5.8       | SYSTEM CONFIGURATIONS                                           |       |

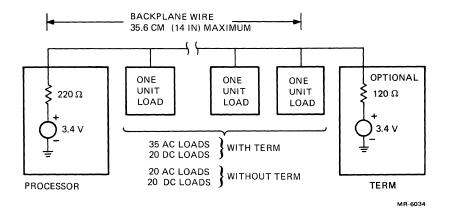

| 5.8.1     | Rules for Configuring Single-Backplane Systems                  | 5-29  |

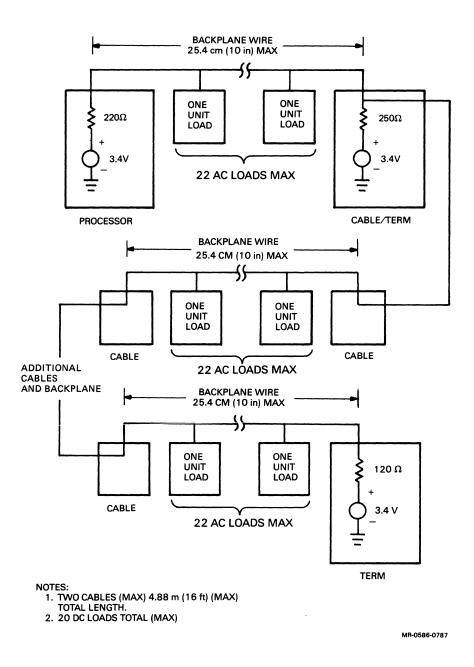

| 5.8.2     | Rules for Configuring Multiple-Backplane Systems                | 5-29  |

| 5.8.3     | Power Supply Loading                                            |       |

| CHAPTER 6 | ADDRESSING MODES AND BASE INSTRUCTION SET                       |       |

| 6.1       | INTRODUCTION                                                    | 6-1   |

| 6.2       | ADDRESSING MODES                                                |       |

| 6.2.1     | Single-Operand Addressing                                       |       |

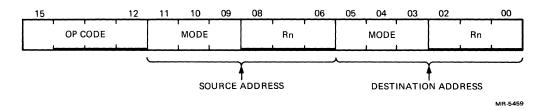

| 6.2.2     | Double-Operand Addressing                                       |       |

| 6.2.3     |                                                                 |       |

|           | Direct Addressing                                               |       |

| 6.2.3.1   | Register Mode                                                   | 6-0   |

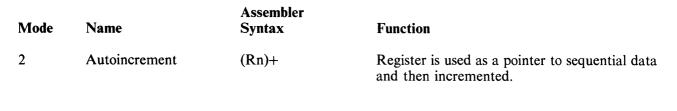

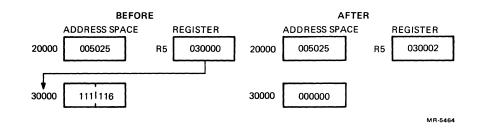

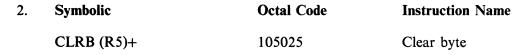

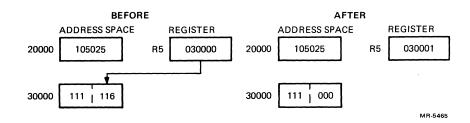

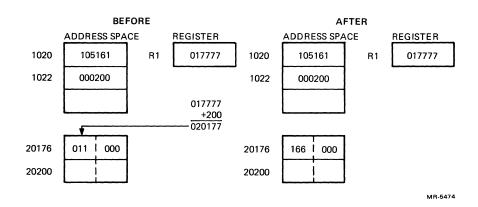

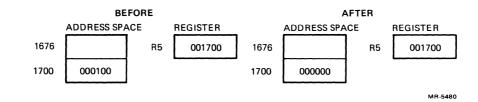

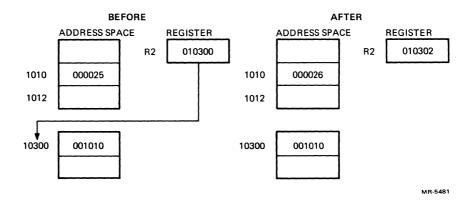

| 6.2.3.2   | Autoincrement Mode [OPR (Rn)+]                                  | 6-7   |

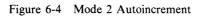

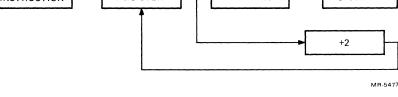

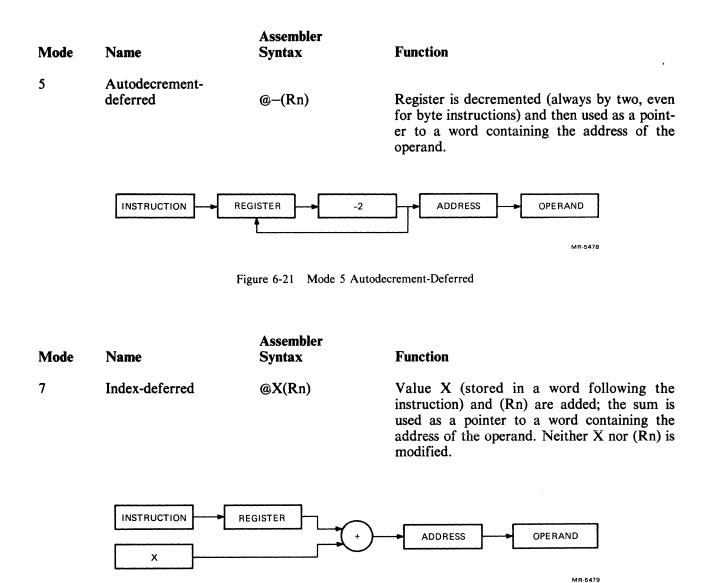

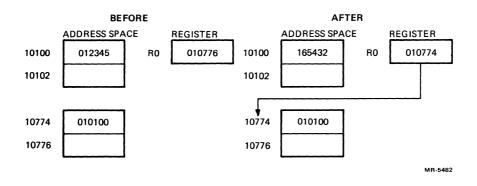

| 6.2.3.3   | Autodecrement Mode [OPR-(Rn)]                                   | 6-9   |

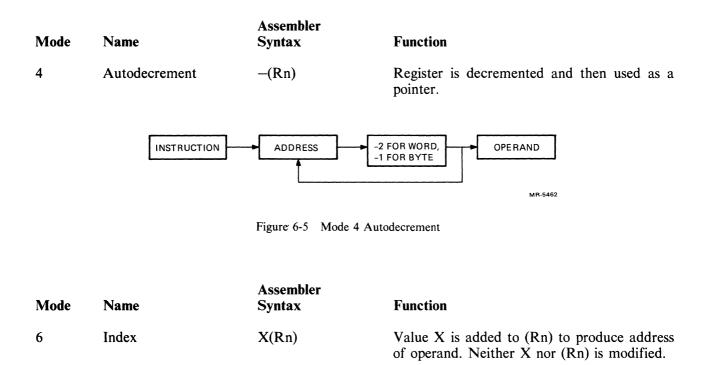

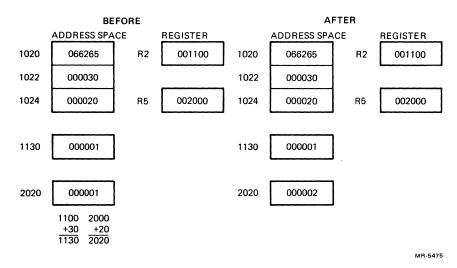

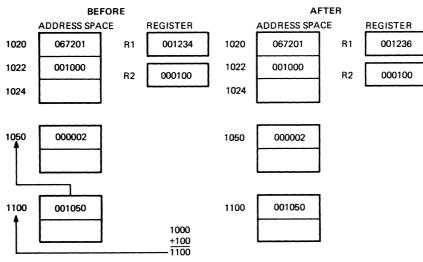

| 6.2.3.4   | Index Mode [OPR X(Rn)]                                          | 6-11  |

| 6.2.4     | Deferred (Indirect) Addressing                                  | 6-13  |

| 6.2.5     | Use Of The PC as a General-Purpose Register                     |       |

| 6.2.5.1   | Immediate Mode [OPR #n,DD]                                      |       |

| 6.2.5.2   | Absolute Addressing Mode [OPR @#A]                              | 6-18  |

| 6.2.5.3   | Relative Addressing Mode [OPR A or OPR X(PC)]                   | 6 20  |

|           | Deleting Defensed Addressing Mode [OPR A OF OPD ON CONTRACTORS] | 0-20  |

| 6.2.5.4   | Relative-Deferred Addressing Mode [OPR @A or OPR @X(PC)]        |       |

| 6.2.6     | Use Of The Stack Pointer as a General-Purpose Register          | 6-21  |

.

| 6.3                                                                                                                                                   | INSTRUCTION SET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6-21                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

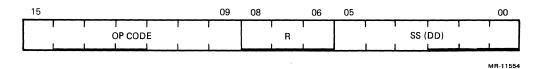

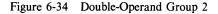

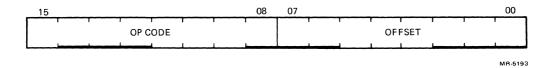

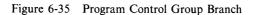

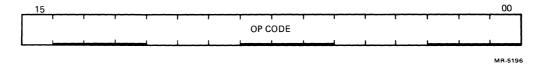

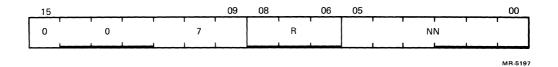

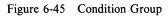

| 6.3.1                                                                                                                                                 | Instruction Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                              |

| 6.3.2                                                                                                                                                 | Byte Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                              |

| 6.3.3                                                                                                                                                 | List Of Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                              |

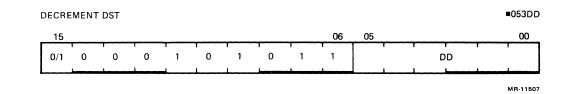

| 6.3.4                                                                                                                                                 | Single-Operand Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                              |

| 6.3.4.1                                                                                                                                               | General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                              |

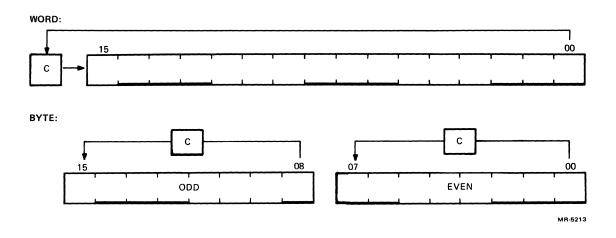

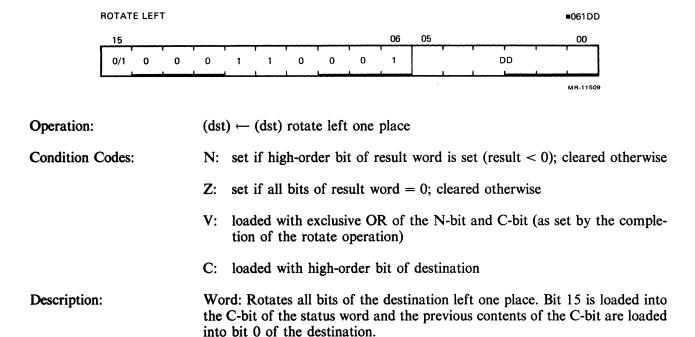

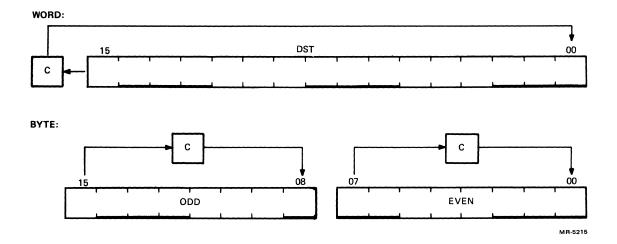

| 6.3.4.2                                                                                                                                               | Shifts And Rotates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                              |

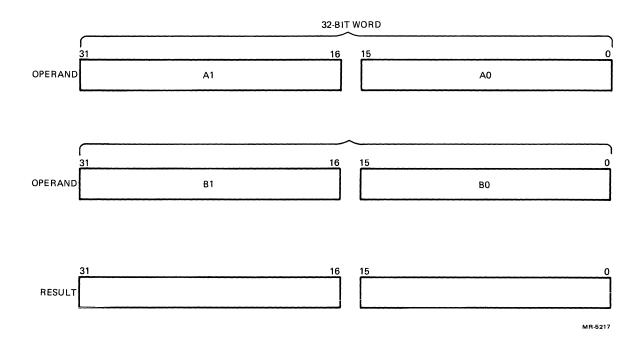

| 6.3.4.3                                                                                                                                               | Multiple-Precision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                              |

| 6.3.4.4                                                                                                                                               | PS Word Operators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                              |

| 6.3.5                                                                                                                                                 | Double-Operand Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                              |

| 6.3.5.1                                                                                                                                               | General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                              |

| 6.3.5.2                                                                                                                                               | Logical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                              |

| 6.3.6                                                                                                                                                 | Program Control Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                              |

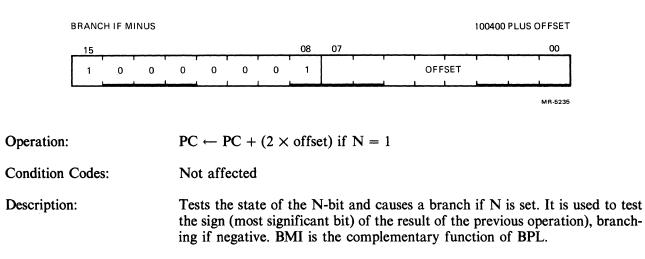

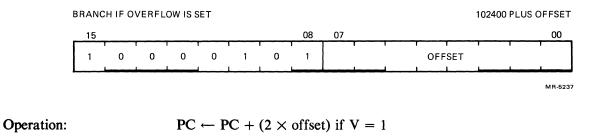

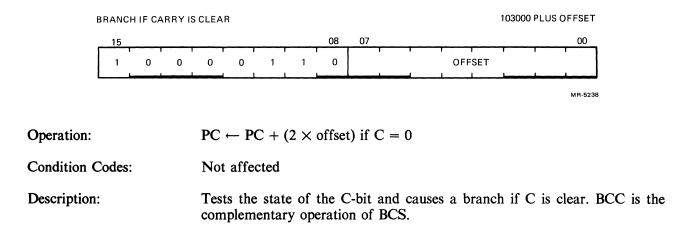

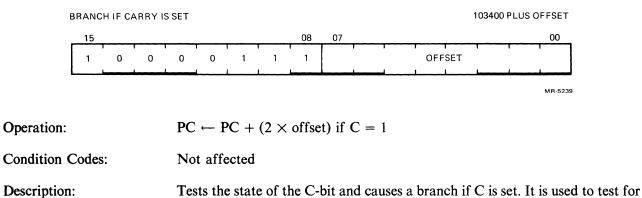

| 6.3.6.1                                                                                                                                               | Branches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                              |

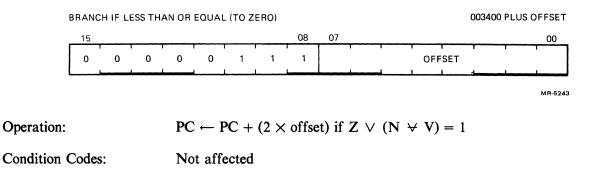

| 6.3.6.2                                                                                                                                               | Signed Conditional Branches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                              |

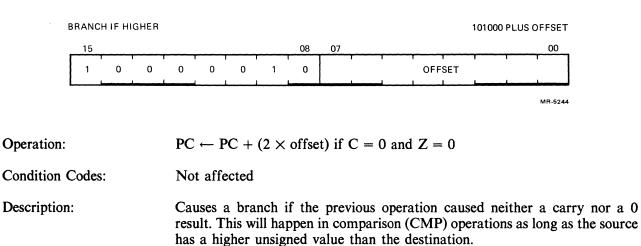

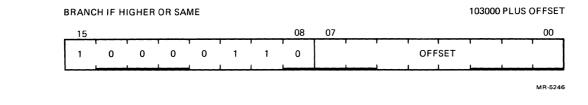

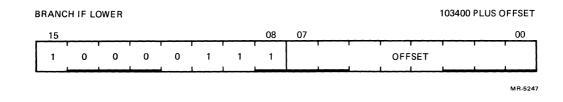

| 6.3.6.3                                                                                                                                               | Unsigned Conditional Branches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                              |

| 6.3.6.4                                                                                                                                               | Jump and Subroutine Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                              |

| 6.3.6.5                                                                                                                                               | Traps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                              |

| 6.3.6.6                                                                                                                                               | Miscellaneous Program Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                              |

| 6.3.6.7                                                                                                                                               | Reserved Instruction Traps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                              |

| 6.3.6.8                                                                                                                                               | Trace Trap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                              |

| 6.3.7                                                                                                                                                 | Miscellaneous Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6-77                                                                                                         |

| 6.3.8                                                                                                                                                 | Condition Code Operators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                              |

| 0.5.0                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0 00                                                                                                         |

|                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                              |

| CHAPTER 7                                                                                                                                             | FLOATING-POINT ARITHMETIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                              |

|                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7-1                                                                                                          |

| 7.1                                                                                                                                                   | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                              |

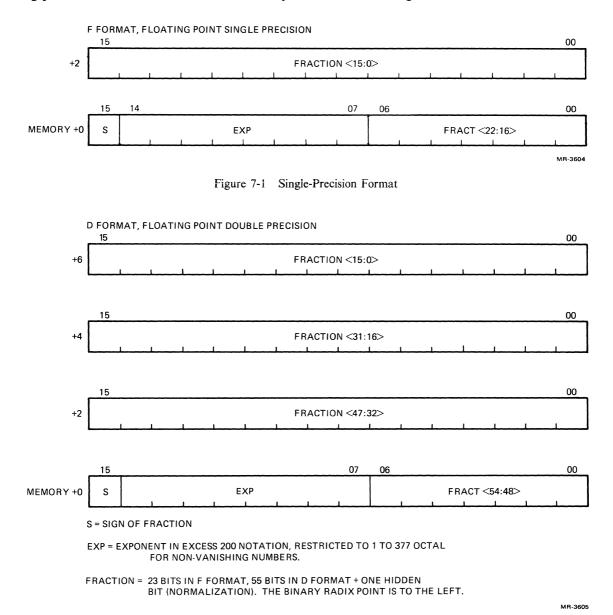

| 7.1<br>7.2                                                                                                                                            | INTRODUCTION<br>FLOATING-POINT DATA FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7-1                                                                                                          |

| 7.1<br>7.2<br>7.2.1                                                                                                                                   | INTRODUCTION<br>FLOATING-POINT DATA FORMATS<br>Nonvanishing Floating-Point Numbers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7-1<br>7-1                                                                                                   |

| 7.1<br>7.2<br>7.2.1<br>7.2.2                                                                                                                          | INTRODUCTION<br>FLOATING-POINT DATA FORMATS<br>Nonvanishing Floating-Point Numbers<br>Floating-Point Zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7-1<br>7-1<br>7-1                                                                                            |

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3                                                                                                                 | INTRODUCTION<br>FLOATING-POINT DATA FORMATS<br>Nonvanishing Floating-Point Numbers<br>Floating-Point Zero<br>Undefined Variables                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7-1<br>7-1<br>7-1<br>7-2                                                                                     |

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4                                                                                                        | INTRODUCTION<br>FLOATING-POINT DATA FORMATS<br>Nonvanishing Floating-Point Numbers.<br>Floating-Point Zero<br>Undefined Variables.<br>Floating-Point Data                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7-1<br>7-1<br>7-1<br>7-2<br>7-2                                                                              |

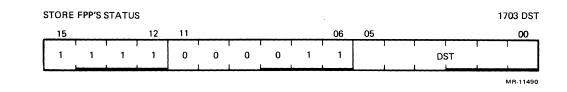

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.3                                                                                                 | INTRODUCTION<br>FLOATING-POINT DATA FORMATS<br>Nonvanishing Floating-Point Numbers.<br>Floating-Point Zero<br>Undefined Variables.<br>Floating-Point Data<br>FLOATING-POINT STATUS REGISTER (FPS)                                                                                                                                                                                                                                                                                                                                                                                           | 7-1<br>7-1<br>7-1<br>7-2<br>7-2<br>7-3                                                                       |

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.3<br>7.4                                                                                          | INTRODUCTION<br>FLOATING-POINT DATA FORMATS<br>Nonvanishing Floating-Point Numbers<br>Floating-Point Zero<br>Undefined Variables<br>Floating-Point Data<br>FLOATING-POINT STATUS REGISTER (FPS)<br>FLOATING EXCEPTION CODE AND ADDRESS REGISTERS                                                                                                                                                                                                                                                                                                                                            | 7-1<br>7-1<br>7-1<br>7-2<br>7-2<br>7-3<br>7-6                                                                |

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.3<br>7.4<br>7.5                                                                                   | INTRODUCTION<br>FLOATING-POINT DATA FORMATS<br>Nonvanishing Floating-Point Numbers<br>Floating-Point Zero<br>Undefined Variables<br>Floating-Point Data<br>FLOATING-POINT STATUS REGISTER (FPS)<br>FLOATING EXCEPTION CODE AND ADDRESS REGISTERS<br>FLOATING-POINT INSTRUCTION ADDRESSING                                                                                                                                                                                                                                                                                                   | 7-1<br>7-1<br>7-2<br>7-2<br>7-2<br>7-3<br>7-6<br>7-7                                                         |

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.3<br>7.4<br>7.5<br>7.6                                                                            | INTRODUCTION<br>FLOATING-POINT DATA FORMATS<br>Nonvanishing Floating-Point Numbers<br>Floating-Point Zero<br>Undefined Variables<br>Floating-Point Data<br>FLOATING-POINT STATUS REGISTER (FPS)<br>FLOATING EXCEPTION CODE AND ADDRESS REGISTERS<br>FLOATING-POINT INSTRUCTION ADDRESSING<br>ACCURACY                                                                                                                                                                                                                                                                                       | 7-1<br>7-1<br>7-2<br>7-2<br>7-2<br>7-3<br>7-6<br>7-7<br>7-7                                                  |

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.3<br>7.4<br>7.5                                                                                   | INTRODUCTION<br>FLOATING-POINT DATA FORMATS<br>Nonvanishing Floating-Point Numbers<br>Floating-Point Zero<br>Undefined Variables<br>Floating-Point Data<br>FLOATING-POINT STATUS REGISTER (FPS)<br>FLOATING EXCEPTION CODE AND ADDRESS REGISTERS<br>FLOATING-POINT INSTRUCTION ADDRESSING                                                                                                                                                                                                                                                                                                   | 7-1<br>7-1<br>7-2<br>7-2<br>7-2<br>7-3<br>7-6<br>7-7<br>7-7                                                  |

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.3<br>7.4<br>7.5<br>7.6                                                                            | INTRODUCTION<br>FLOATING-POINT DATA FORMATS<br>Nonvanishing Floating-Point Numbers<br>Floating-Point Zero<br>Undefined Variables<br>Floating-Point Data<br>FLOATING-POINT STATUS REGISTER (FPS)<br>FLOATING EXCEPTION CODE AND ADDRESS REGISTERS<br>FLOATING-POINT INSTRUCTION ADDRESSING<br>ACCURACY                                                                                                                                                                                                                                                                                       | 7-1<br>7-1<br>7-2<br>7-2<br>7-2<br>7-3<br>7-6<br>7-7<br>7-7                                                  |

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br><b>CHAPTER 8</b>                                                 | INTRODUCTION<br>FLOATING-POINT DATA FORMATS<br>Nonvanishing Floating-Point Numbers<br>Floating-Point Zero<br>Undefined Variables<br>Floating-Point Data<br>FLOATING-POINT STATUS REGISTER (FPS)<br>FLOATING EXCEPTION CODE AND ADDRESS REGISTERS<br>FLOATING-POINT INSTRUCTION ADDRESSING<br>ACCURACY<br>FLOATING-POINT INSTRUCTIONS<br><b>PROGRAMMING TECHNIQUES</b>                                                                                                                                                                                                                       | 7-1<br>7-1<br>7-2<br>7-2<br>7-3<br>7-6<br>7-7<br>7-8                                                         |

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br><b>CHAPTER 8</b><br>8.1                                          | INTRODUCTION<br>FLOATING-POINT DATA FORMATS<br>Nonvanishing Floating-Point Numbers<br>Floating-Point Zero<br>Undefined Variables<br>Floating-Point Data<br>FLOATING-POINT STATUS REGISTER (FPS)<br>FLOATING EXCEPTION CODE AND ADDRESS REGISTERS<br>FLOATING-POINT INSTRUCTION ADDRESSING<br>ACCURACY<br>FLOATING-POINT INSTRUCTIONS<br><b>PROGRAMMING TECHNIQUES</b><br>INTRODUCTION                                                                                                                                                                                                       | 7-1<br>7-1<br>7-2<br>7-2<br>7-3<br>7-6<br>7-7<br>7-7<br>7-8                                                  |

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br><b>CHAPTER 8</b><br>8.1<br>8.2                                   | INTRODUCTION<br>FLOATING-POINT DATA FORMATS<br>Nonvanishing Floating-Point Numbers<br>Floating-Point Zero<br>Undefined Variables<br>Floating-Point Data<br>FLOATING-POINT STATUS REGISTER (FPS)<br>FLOATING EXCEPTION CODE AND ADDRESS REGISTERS<br>FLOATING-POINT INSTRUCTION ADDRESSING<br>ACCURACY<br>FLOATING-POINT INSTRUCTIONS<br><b>PROGRAMMING TECHNIQUES</b><br>INTRODUCTION<br>POSITION-INDEPENDENT CODE                                                                                                                                                                          | 7-1<br>7-1<br>7-2<br>7-2<br>7-3<br>7-6<br>7-7<br>7-7<br>7-8                                                  |

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br><b>CHAPTER 8</b><br>8.1<br>8.2<br>8.2.1                          | INTRODUCTION<br>FLOATING-POINT DATA FORMATS<br>Nonvanishing Floating-Point Numbers<br>Floating-Point Zero<br>Undefined Variables<br>Floating-Point Data<br>FLOATING-POINT STATUS REGISTER (FPS)<br>FLOATING EXCEPTION CODE AND ADDRESS REGISTERS<br>FLOATING-POINT INSTRUCTION ADDRESSING<br>ACCURACY<br>FLOATING-POINT INSTRUCTIONS<br>PROGRAMMING TECHNIQUES<br>INTRODUCTION<br>POSITION-INDEPENDENT CODE<br>Use of Addressing Modes in the Construction of Position-Independent Code                                                                                                     | 7-1<br>7-1<br>7-2<br>7-2<br>7-3<br>7-3<br>7-6<br>7-7<br>7-8<br>8-1<br>8-1<br>8-1                             |

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br><b>CHAPTER 8</b><br>8.1<br>8.2<br>8.2.1<br>8.2.1<br>8.2.2        | INTRODUCTION<br>FLOATING-POINT DATA FORMATS<br>Nonvanishing Floating-Point Numbers<br>Floating-Point Zero<br>Undefined Variables<br>Floating-Point Data<br>FLOATING-POINT STATUS REGISTER (FPS)<br>FLOATING EXCEPTION CODE AND ADDRESS REGISTERS<br>FLOATING-POINT INSTRUCTION ADDRESSING<br>ACCURACY<br>FLOATING-POINT INSTRUCTIONS<br>PROGRAMMING TECHNIQUES<br>INTRODUCTION<br>POSITION-INDEPENDENT CODE<br>Use of Addressing Modes in the Construction of Position-Independent Code<br>Comparison of Position-Dependent and Position-Independent Code                                   | 7-1<br>7-1<br>7-1<br>7-2<br>7-2<br>7-3<br>7-6<br>7-7<br>7-7<br>7-8<br>8-1<br>8-1<br>8-3                      |

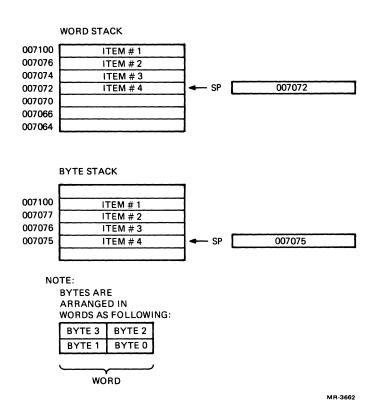

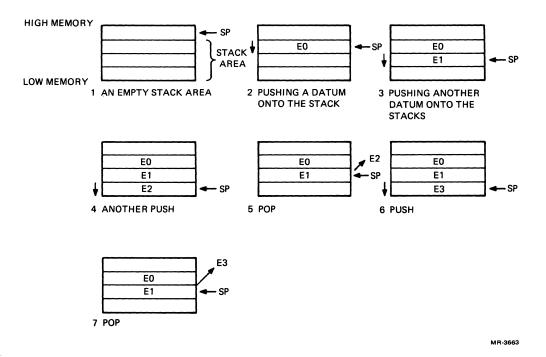

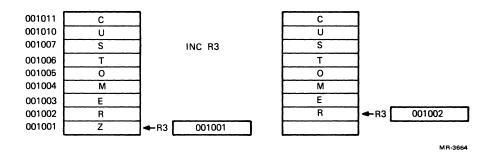

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br><b>CHAPTER 8</b><br>8.1<br>8.2<br>8.2.1<br>8.2.2<br>8.3          | INTRODUCTION<br>FLOATING-POINT DATA FORMATS<br>Nonvanishing Floating-Point Numbers<br>Floating-Point Zero<br>Undefined Variables<br>Floating-Point Data<br>FLOATING-POINT STATUS REGISTER (FPS)<br>FLOATING EXCEPTION CODE AND ADDRESS REGISTERS<br>FLOATING-POINT INSTRUCTION ADDRESSING<br>ACCURACY<br>FLOATING-POINT INSTRUCTIONS<br>PROGRAMMING TECHNIQUES<br>INTRODUCTION<br>POSITION-INDEPENDENT CODE<br>Use of Addressing Modes in the Construction of Position-Independent Code<br>Comparison of Position-Dependent and Position-Independent Code                                   | 7-1<br>7-1<br>7-2<br>7-2<br>7-3<br>7-6<br>7-7<br>7-7<br>7-8<br>8-1<br>8-1<br>8-3<br>8-5                      |

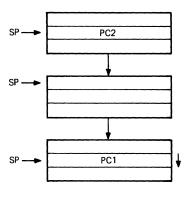

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br><b>CHAPTER 8</b><br>8.1<br>8.2<br>8.2.1<br>8.2.2<br>8.3<br>8.3.1 | INTRODUCTION<br>FLOATING-POINT DATA FORMATS<br>Nonvanishing Floating-Point Numbers<br>Floating-Point Zero<br>Undefined Variables<br>Floating-Point Data<br>FLOATING-POINT STATUS REGISTER (FPS)<br>FLOATING EXCEPTION CODE AND ADDRESS REGISTERS<br>FLOATING-POINT INSTRUCTION ADDRESSING<br>ACCURACY<br>FLOATING-POINT INSTRUCTIONS<br>PROGRAMMING TECHNIQUES<br>INTRODUCTION<br>POSITION-INDEPENDENT CODE<br>Use of Addressing Modes in the Construction of Position-Independent Code<br>Comparison of Position-Dependent and Position-Independent Code<br>STACKS<br>Pushing onto a Stack | 7-1<br>7-1<br>7-2<br>7-2<br>7-3<br>7-6<br>7-7<br>7-7<br>7-8<br>8-1<br>8-1<br>8-3<br>8-5<br>8-6               |

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br><b>CHAPTER 8</b><br>8.1<br>8.2<br>8.2.1<br>8.2.2<br>8.3          | INTRODUCTION<br>FLOATING-POINT DATA FORMATS<br>Nonvanishing Floating-Point Numbers<br>Floating-Point Zero<br>Undefined Variables<br>Floating-Point Data<br>FLOATING-POINT STATUS REGISTER (FPS)<br>FLOATING EXCEPTION CODE AND ADDRESS REGISTERS<br>FLOATING-POINT INSTRUCTION ADDRESSING<br>ACCURACY<br>FLOATING-POINT INSTRUCTIONS<br>PROGRAMMING TECHNIQUES<br>INTRODUCTION<br>POSITION-INDEPENDENT CODE<br>Use of Addressing Modes in the Construction of Position-Independent Code<br>Comparison of Position-Dependent and Position-Independent Code                                   | 7-1<br>7-1<br>7-2<br>7-2<br>7-3<br>7-6<br>7-7<br>7-7<br>7-8<br>8-1<br>8-1<br>8-1<br>8-3<br>8-5<br>8-6<br>8-6 |

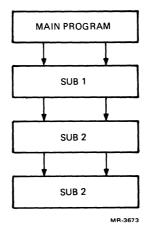

| 8.3.6      | Subroutine Linkage                      | . 8-10 |

|------------|-----------------------------------------|--------|

| 8.3.6.1    | Return from a Subroutine                |        |

| 8.3.6.2    | Subroutine Advantages                   |        |

| 8.3.7      | Interrupts                              |        |

| 8.3.7.1    | Interrupt Service Routines              |        |

| 8.3.7.2    | Nesting                                 |        |

| 8.3.8      | Reentrancy                              |        |

| 8.3.8.1    | Reentrant Code                          |        |

| 8.3.8.2    | Writing Reentrant Code                  | . 8-14 |

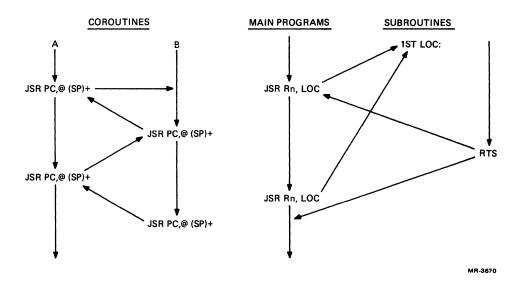

| 8.3.9      | Coroutines                              |        |

| 8.3.9.1    | Coroutine Calls                         |        |

| 8.3.9.2    | Coroutines Versus Subroutines           |        |

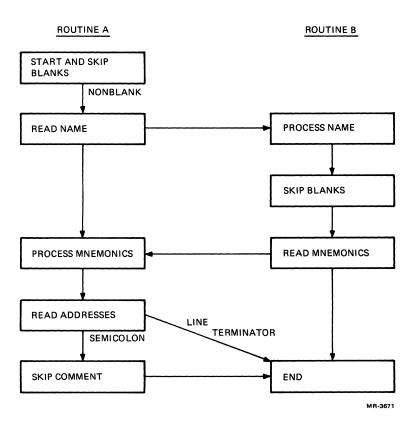

| 8.3.9.3    | Using Coroutines                        |        |

| 8.3.10     | Recursion                               |        |

| 8.3.11     | Processor Traps                         |        |

| 8.3.11.1   | Trap Instructions                       |        |

| 8.3.11.2   | Use of Macro Calls                      |        |

| 8.3.12     | Conversion Routines                     |        |

| 8.4        | PROGRAMMING THE PROCESSOR STATUS WORD   | 8-26   |

| 8.5        | PROGRAMMING PERIPHERALS                 | 8-27   |

| 8.6        | PDP-11 PROGRAMMING EXAMPLES             | 8-27   |

| 8.7        | LOOPING TECHNIQUES                      |        |

| CHAPTER 9  | BOOT ROMS AND DIAGNOSTICS               |        |

| 9.1        | INTRODUCTION                            |        |

| 9.2        | MXV11-B2 ROM SET                        |        |

| 9.2.1      | Power-Up                                |        |

| 9.2.2      | Automatic Booting                       |        |

| 9.2.3      | Manual Booting                          |        |

| 9.2.4      | Error and Help Messages                 |        |

| 9.3        | DIAGNOSTICS                             |        |

| 9.4        | DIAGNOSTIC EXAMPLE                      | 9-7    |

| APPENDIX A | INSTRUCTION TIMING                      |        |

| A.1        | GENERAL                                 | A-1    |

| A.2        | BASE INSTRUCTION SET TIMING             | A-1    |

| A.3        | FLOATING-POINT INSTRUCTION SET TIMING   |        |

| APPENDIX B | PROGRAMMING DIFFERENCES                 |        |

| APPENDIX C | CONFIGURATION NOTES                     |        |

| C.1        | GENERAL                                 | . C-1  |

| C.2        | KDJ11-A CPU MODULE CONFIGURATION NOTES. |        |

| C.3        | FPJ11-AA FPA CONFIGURATION NOTES.       |        |

|            | -                                       |        |

# **FIGURES**

Figure No.

# Title

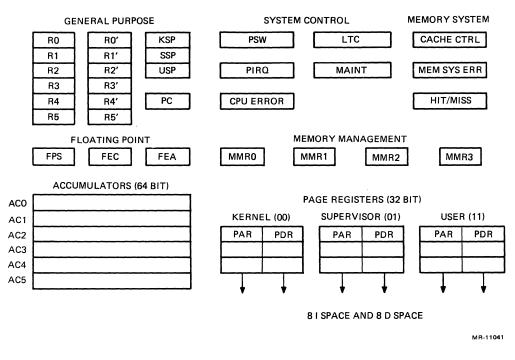

| 1-1  | Programming Model                                  |        |

|------|----------------------------------------------------|--------|

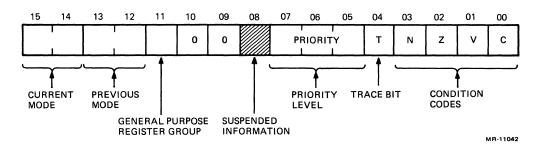

| 1-2  | Processor Status Register                          |        |

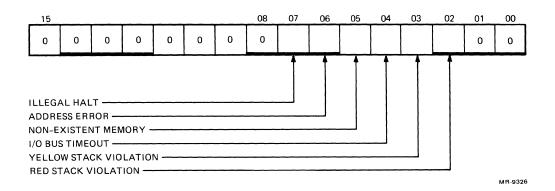

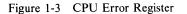

| 1-3  | CPU Error Register                                 |        |

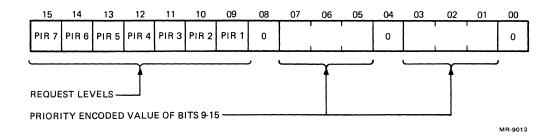

| 1-4  | Program Interrupt Request Register (PIRQ)1-6       |        |

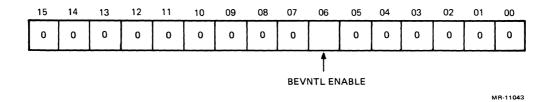

| 1-5  | Line Time Clock Register (BEVNT)                   |        |

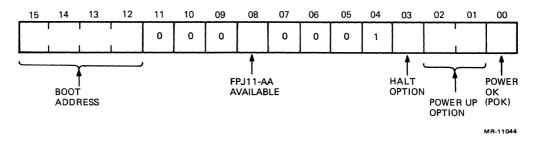

| 1-6  | Maintenance Register1-7                            |        |

| 1-8  | 18-Bit Mapping1-11                                 |        |

| 1-9  | 22-Bit Mapping1-12                                 |        |

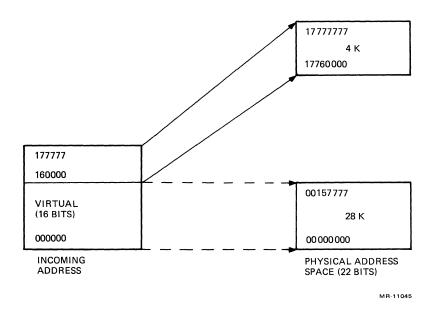

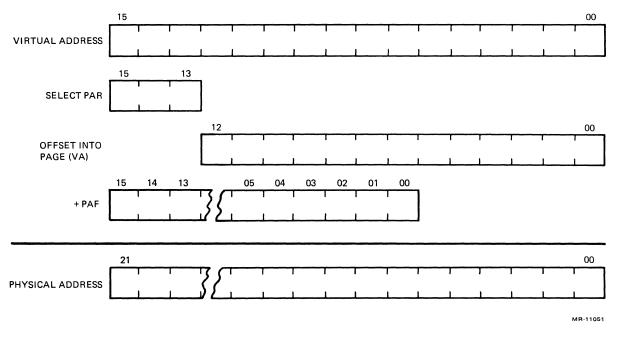

| 1-10 | Virtual Address Mapping into Physical Address 1-13 |        |

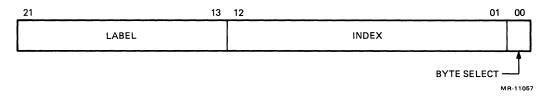

| 1-11 | Interpretation of a Virtual Address1-14            | ŀ      |

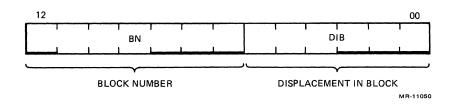

| 1-12 | Displacement Field of a Virtual Address1-14        |        |

| 1-13 | Construction of a Physical Address 1-15            | )      |

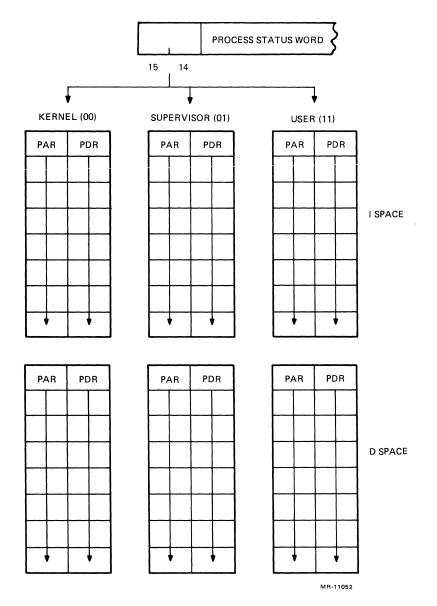

| 1-14 | Active Page Registers1-16                          | )      |

| 1-15 | Page Address Register (PAR)1-18                    | ;      |

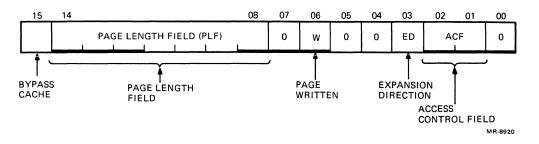

| 1-16 | Page Descriptor Register (PDR)1-18                 | ;      |

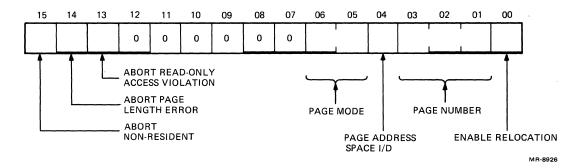

| 1-17 | Memory Management Register 0 (MMR0)1-20            | )      |

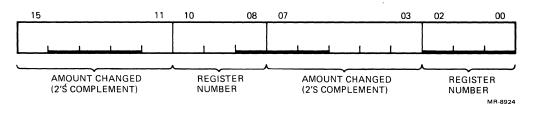

| 1-18 | Memory Management Register 1 (MMR1)1-21            |        |

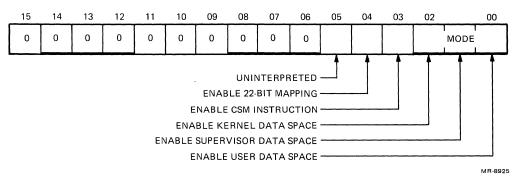

| 1-19 | Memory Management Register 3 (MMR3)1-21            |        |

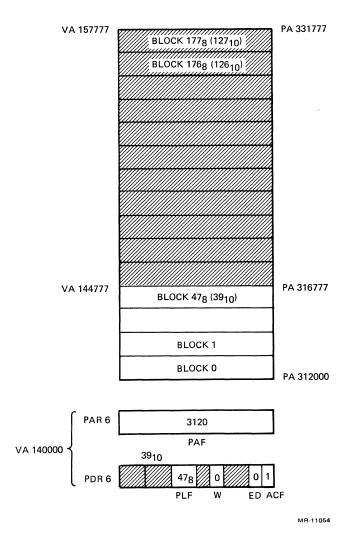

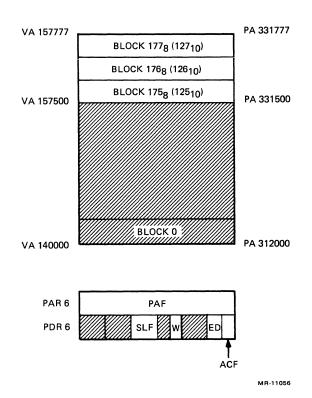

| 1-20 | Typical Memory Page                                |        |

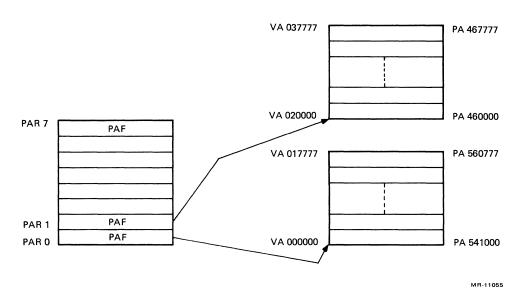

| 1-21 | Nonconsecutive Memory Pages                        |        |

| 1-22 | Typical Stack Memory Page                          |        |

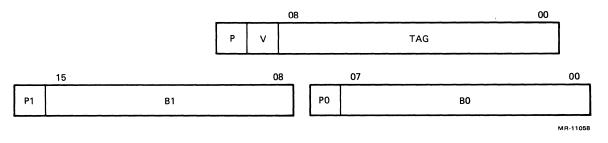

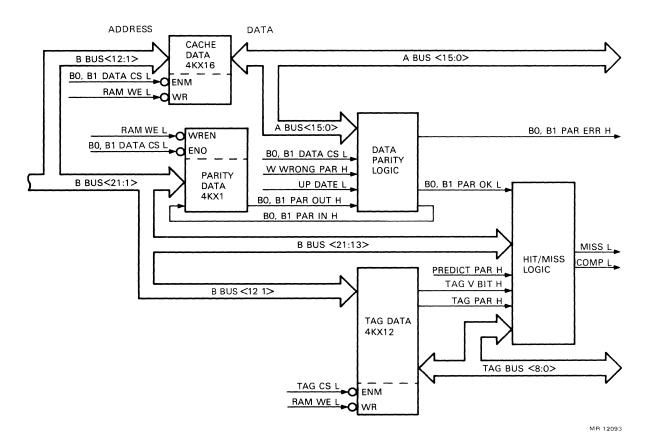

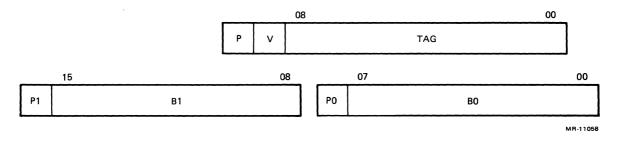

| 1-23 | Cache Physical Address                             |        |

| 1-24 | Cache Data Format                                  |        |

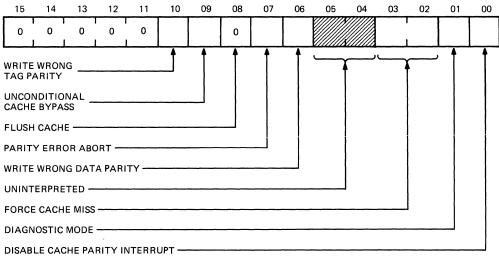

| 1-25 | Cache Control Register (CCR)                       |        |

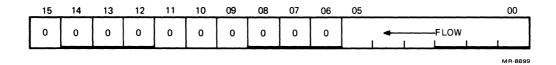

| 1-26 | Hit/Miss Register (HMR)                            |        |

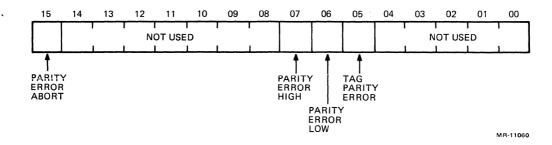

| 1-27 | Memory System Error Register (MSER)                | ,      |

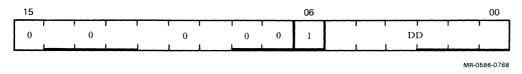

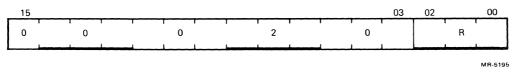

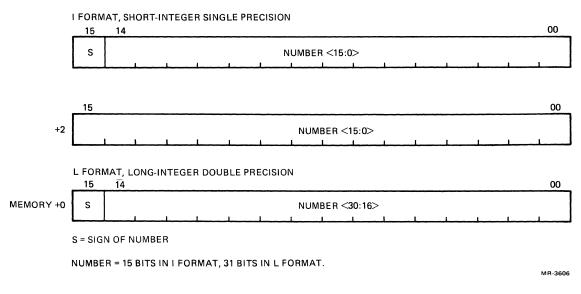

| 1-28 | Single-Precision Format                            |        |

| 1-29 | Double-Precision Format                            |        |

| 1-30 |                                                    |        |

| 1-31 | 2's Complement Format                              |        |

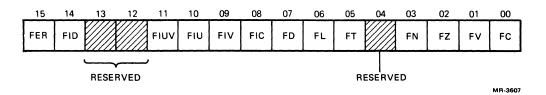

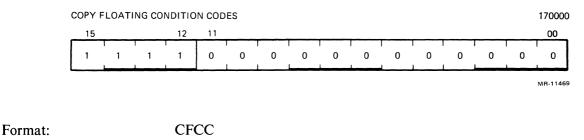

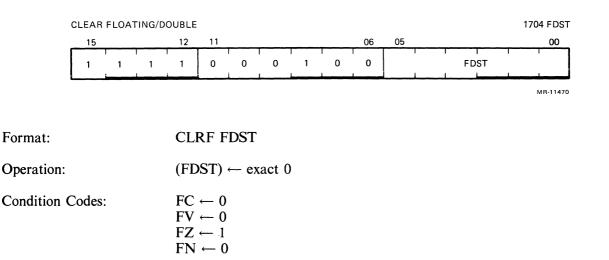

|      | Floating-Point Status Register                     | )<br>I |

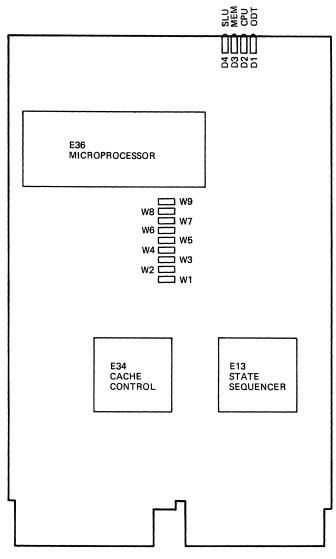

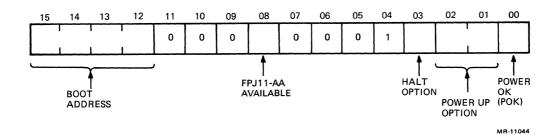

| 2-1  | KDJ11-A Jumper Locations                           |        |

| 2-2  | Maintenance Register                               |        |

| 2-3  | KDJ11-A Power-Up Sequence                          |        |

| 2-4  | KDJ11-A Power-Down Sequence                        |        |

| 2-5  | Micro-ODT Exit Sequence                            |        |

| 2-6  | KDJ11-A Module Contacts                            |        |

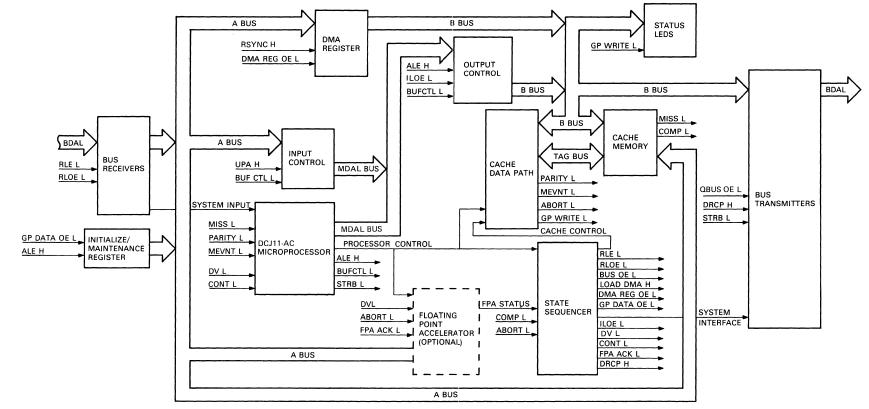

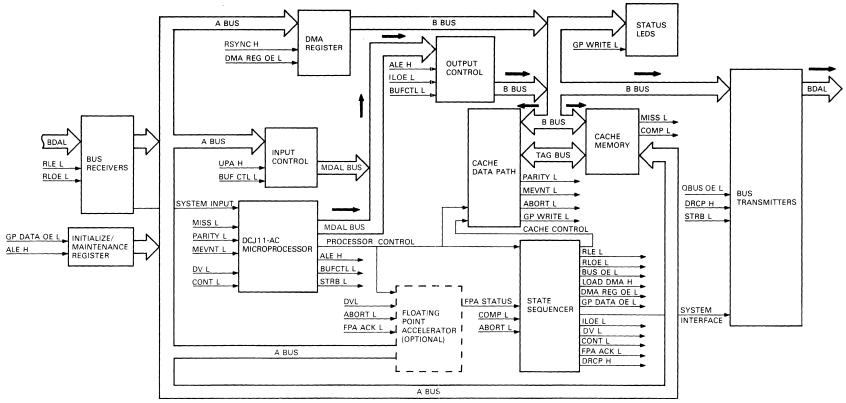

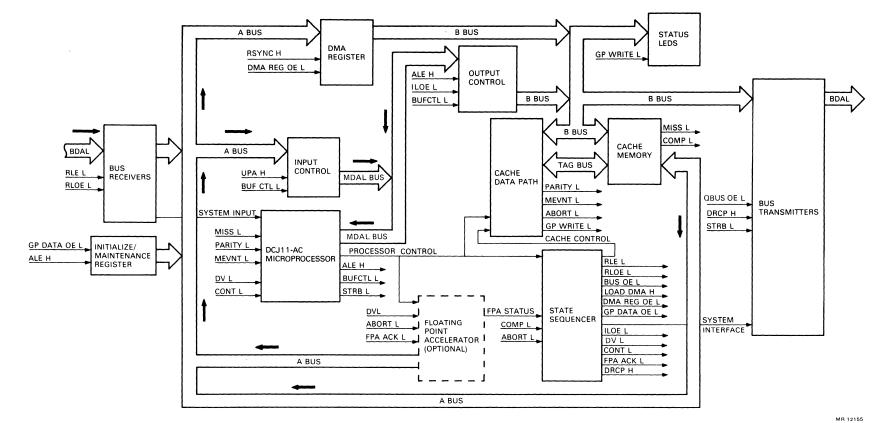

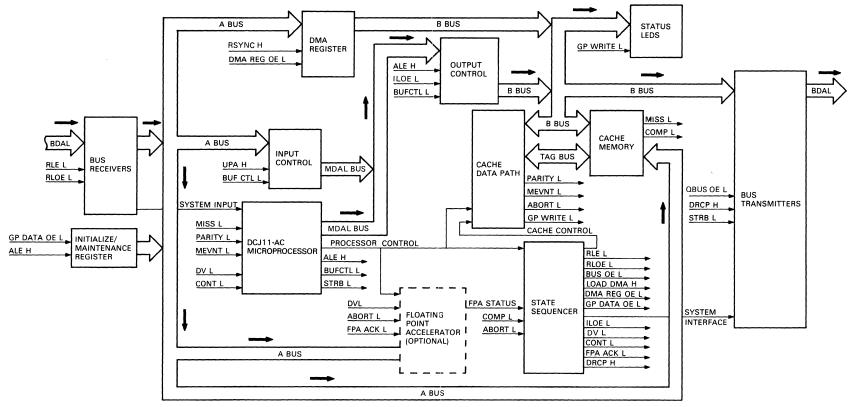

| 4-1  | Functional Block Diagram                           |        |

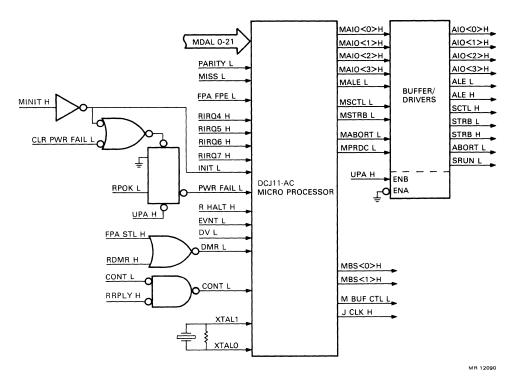

| 4-2  | DCJ11-A Microprocessor                             |        |

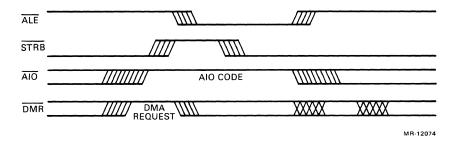

| 4-3  | NOP Transaction                                    |        |

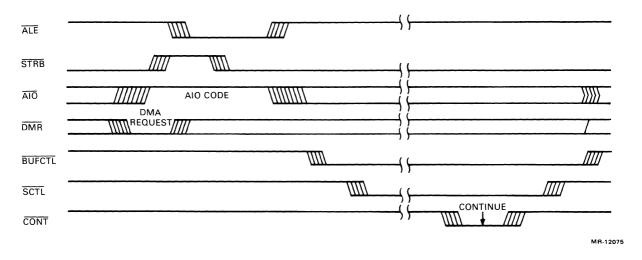

| 4-4  | Stretched NOP Transaction                          |        |

| 4-5  | Bus Read Transaction                               |        |

| 4-6  | Stretched Bus Read Transaction 4-8                 |        |

| 4-7  | Bus Write Transaction                              |        |

| 4-8  | General-Purpose Read Transaction 4-9               |        |

| 4-9  | General-Purpose Write Transaction                  |        |

| 4-10 | Interrupt Acknowledge Transaction                  |        |

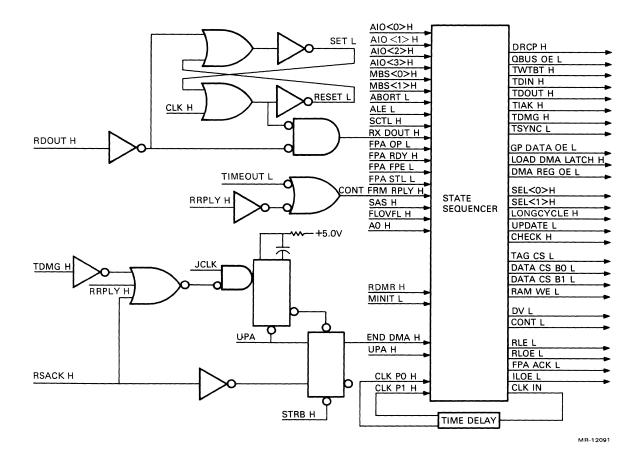

| 4-11 | State Sequencer                                    |        |

| 4-12 | Address Traffic Pattern                            | ŀ      |

| 4-13 | Read Data Busing                                   | ś      |

| 4-14 | Write Data Busing                                  | ;<br>; |

# **FIGURES (Cont)**

Title

Figure No.

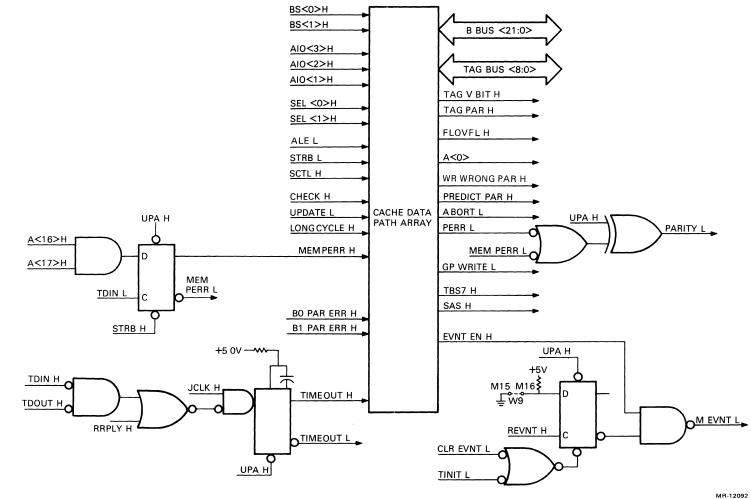

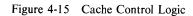

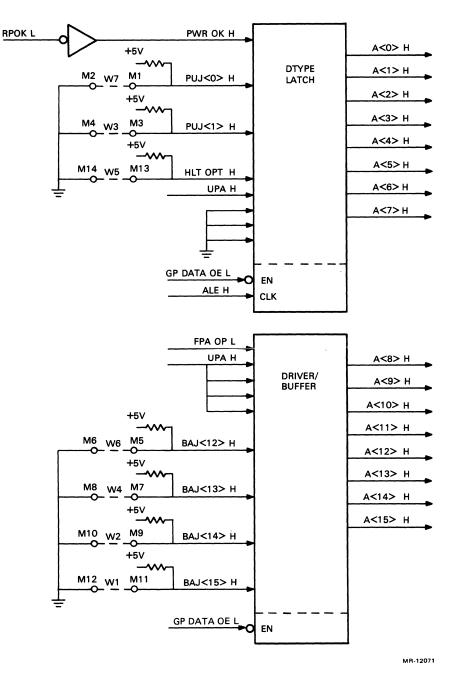

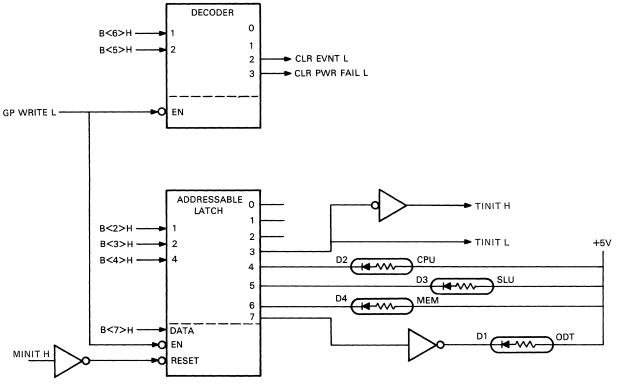

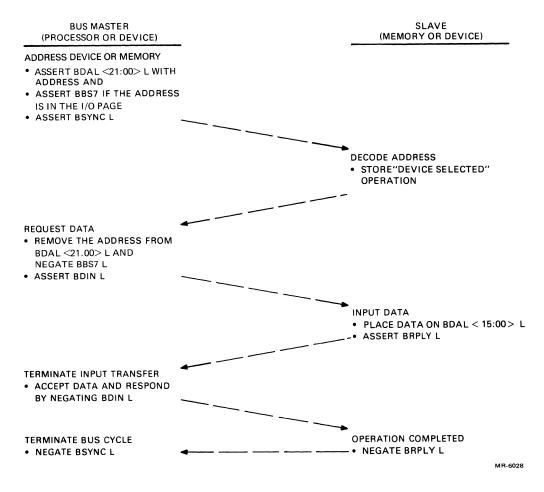

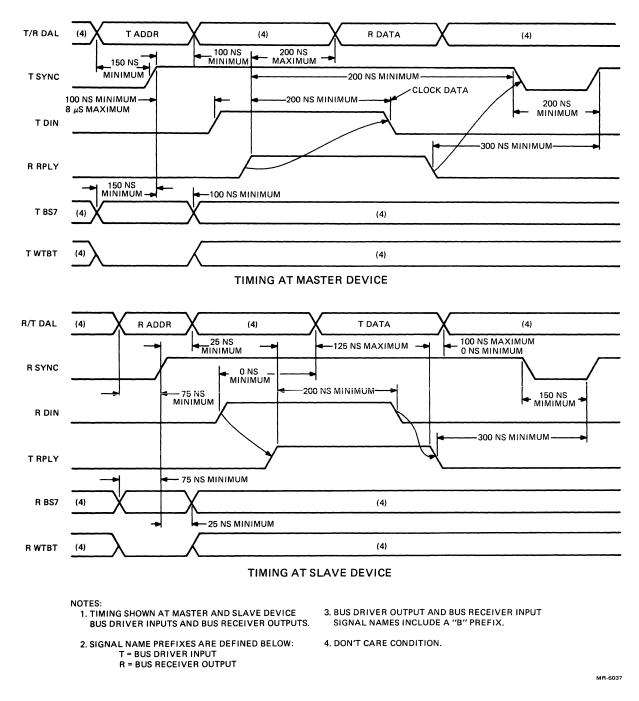

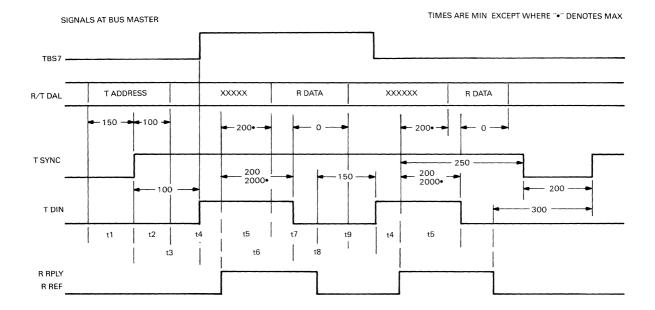

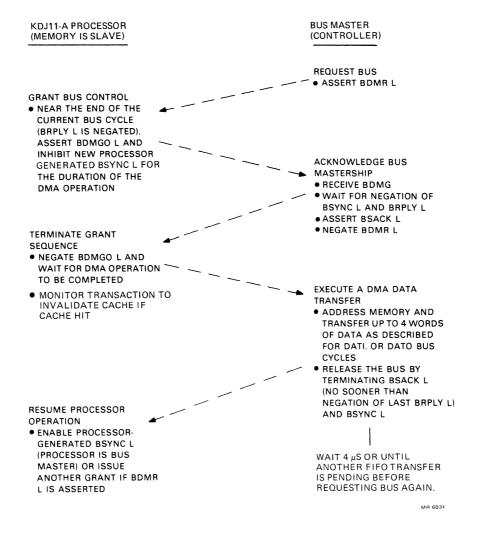

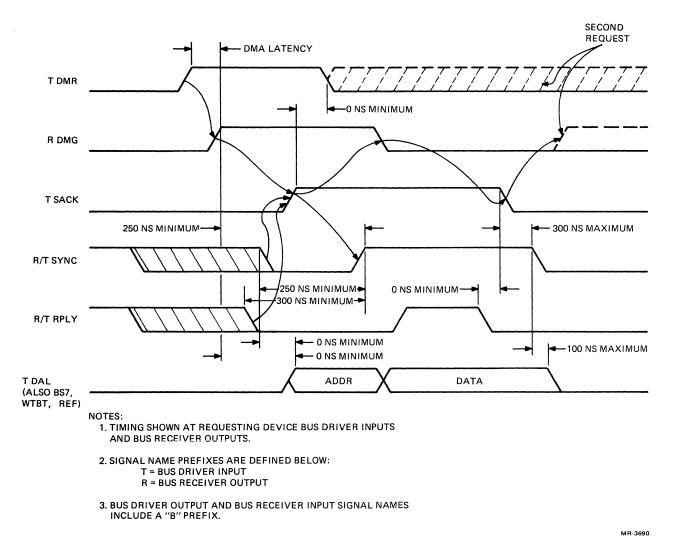

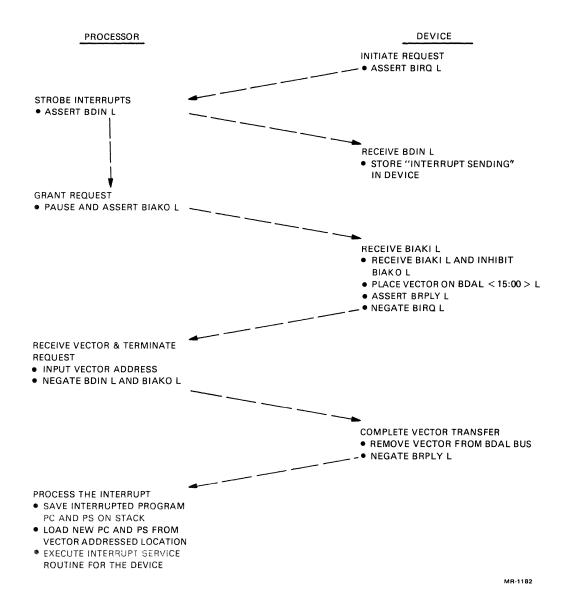

| 415       Cache Control Logic       418         416       Cache Memory       421         417       Cache Memory Physical Address.       422         418       Cache Data Parity Logic       422         419       Cache Data Parity Logic       423         420       Cache HIT/MISS Logic       424         421       KDJ11-A Bus Receivers.       424         422       KDJ11-A Bus Transmitters.       426         423       DCJ11-A Output Control.       426         424       DCJ11-A Input Control.       426         425       DCJ11-A Input Control.       426         427       Status LEDs Logic       429         51       DATI Bus Cycle.       55         52       DATI Bus Cycle.       54         53       DATO or DATO(B) Bus Cycle.       54         54       DATI O or DATO(B) Bus Cycle.       510         55       DATIO Bus Cycle Timing.       511         57       DATI Bus Cycle Timing.       514         58       ADTO or DATO(B) Bus Cycle Timing.       511         57       DATI Bus Cycle Timing.       515         58       DATB Bus Cycle Timing.       515         510       DMA Request                                                                                                                                    | 4.1.5 |                                           | 4 10   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------------------|--------|

| 4-17       Cache Memory Physical Address.       4-22         4-18       Cache Data       4-22         4-19       Cache Data Parity Logic.       4-23         4-20       Cache HIT/MISS Logic.       4-24         4-21       KDJ11-A Bus Receivers.       4-24         4-22       KDJ11-A Bus Transmitters.       4-26         4-23       DCJ11-A Input Control.       4-26         4-24       DCJ11-A Output Control.       4-26         4-25       DMA Monitor Register       4-27         4-26       Initialization/Maintenance Register Logic.       4-28         4-27       Status LEDs Logie       4-29         5-1       DATI Bus Cycle.       5-5         5-2       DATI Bus Cycle Timing.       5-6         5-3       DATO or DATO(B) Bus Cycle.       5-8         5-4       DATO or DATO(B) Bus Cycle.       5-10         5-5       DATIO or DATO(B) Bus Cycle.       5-10         5-6       DATIO or DATO(B) Bus Cycle Timing.       5-11         5-7       DATBI Bus Cycle Timing.       5-13         5-8       DATBO Bus Cycle Timing.       5-14         5-9       DMA Request/Grant Sequence       5-15         5-10       DMA Request/Grant Sequence <td></td> <td></td> <td></td>                                                             |       |                                           |        |

| 4-18       Cache Data       4-22         4-19       Cache Data Parity Logic.       4-23         4-20       Cache HIT/MISS Logic.       4-24         4-21       KDJ11-A Bus Receivers.       4-24         4-21       KDJ11-A Bus Transmitters       4-25         4-23       DCJ11-A Output Control.       4-26         4-24       DCJ11-A Input Control.       4-26         4-25       DMA Monitor Register       4-27         4-26       Initialization/Maintenance Register Logic.       4-28         4-27       Status LEDs Logic       4-29         5-1       DATI Bus Cycle Timing.       5-5         5-2       DATI Bus Cycle Timing.       5-5         5-3       DATO or DATO(B) Bus Cycle.       5-9         5-4       DATO or DATO(B) Bus Cycle.       5-9         5-5       DATIO or DATIO(B) Bus Cycle.       5-10         5-6       DATIO or DATIO(B) Bus Cycle.       5-11         5-7       DATB Bus Cycle Timing.       5-13         5-8       DATBO Bus Cycle Timing.       5-14         5-9       DMA Request/Grant Bus Cycle Timing.       5-15         5-10       DMA Request/Grant Bus Cycle Timing.       5-15         5-10       DMA Request/Gran                                                                                        |       |                                           |        |

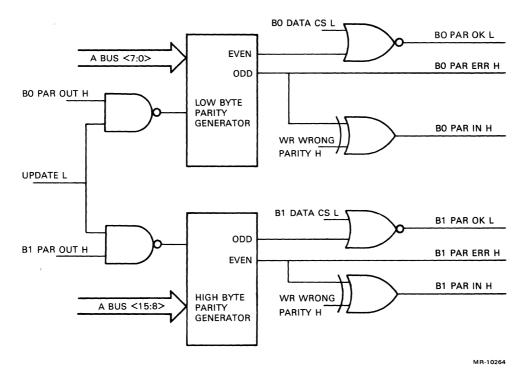

| 4-19       Cache Data Parity Logic.       4-23         4-20       Cache HIT/MISS Logic.       4-24         4-21       KDJ11-A Bus Receivers.       4-24         4-22       KDJ11-A Bus Receivers.       4-24         4-22       KDJ11-A Output Control.       4-26         4-24       DCJ11-A Output Control.       4-26         4-25       DMA Monitor Register       4-27         4-26       Initialization/Maintenance Register Logic.       4-28         4-27       Status LEDs Logic       4-28         4-27       Status LEDs Logic       4-29         5-1       DATI Bus Cycle.       5-6         5-2       DATI Bus Cycle Timing.       5-9         5-3       DATO or DATO(B) Bus Cycle.       5-8         5-4       DATIO or DATIO(B) Bus Cycle Timing.       5-10         5-5       DATIO or DATIO(B) Bus Cycle Timing.       5-11         5-7       DATIB Bus Cycle Timing.       5-13         5-8       DATIO or DATIO(B) Bus Cycle Timing.       5-15         5-10       DMA Request/Grant Bus Cycle Timing.       5-16         5-11       Interrupt Request/Acknowledge Sequence.       5-18         5-12       Interrupt Protocol Timing.       5-21         5-1                                                                               |       |                                           |        |

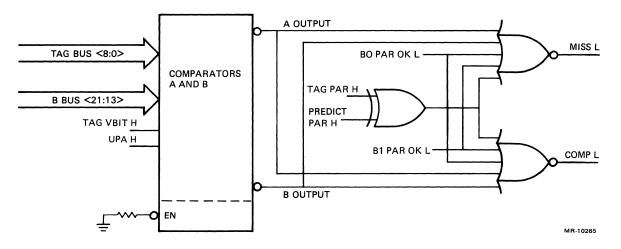

| 4-20       Cache HIT/MISS Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       | Cache Data                                | . 4-22 |

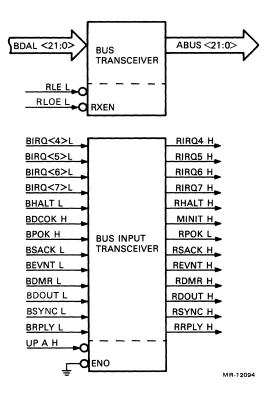

| 4-21         KDJ11-A Bus Receivers.         4-24           4-22         KDJ11-A Bus Transmitters.         4-25           4-23         DCJ11-A Output Control.         4-26           4-24         DCJ11-A Input Control.         4-26           4-25         DMA Monitor Register         4-27           4-26         Initialization/Maintenance Register Logic.         4-28           4-27         Status LEDs Logic         4-28           4-27         DATI Bus Cycle         5-5           5-2         DATI Bus Cycle         5-6           5-3         DATO or DATO(B) Bus Cycle.         5-6           5-4         DATO or DATO(B) Bus Cycle Timing.         5-9           5-5         DATI O or DATIO(B) Bus Cycle Timing.         5-11           5-6         DATIO or DATIO(B) Bus Cycle Timing.         5-13           5-7         DATBI Bus Cycle Timing.         5-13           5-8         DATBO Bus Cycle Timing.         5-14           5-9         DMA Request/Grant Sequence         5-15           5-10         DMA Request/Grant Sequence         5-16           5-11         Interrupt Protocol Timing.         5-17           5-13         Position-Independent Configuration.         5-23           5-14 <td></td> <td></td> <td></td> |       |                                           |        |

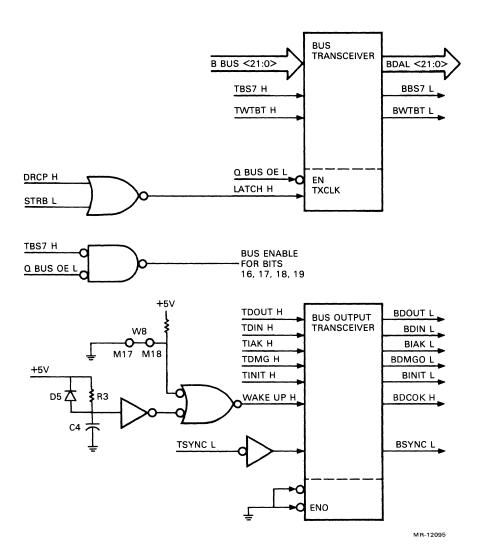

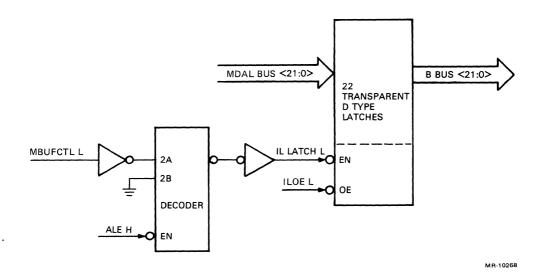

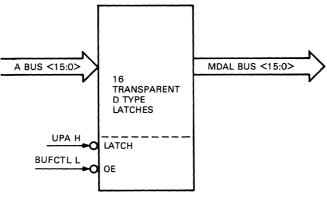

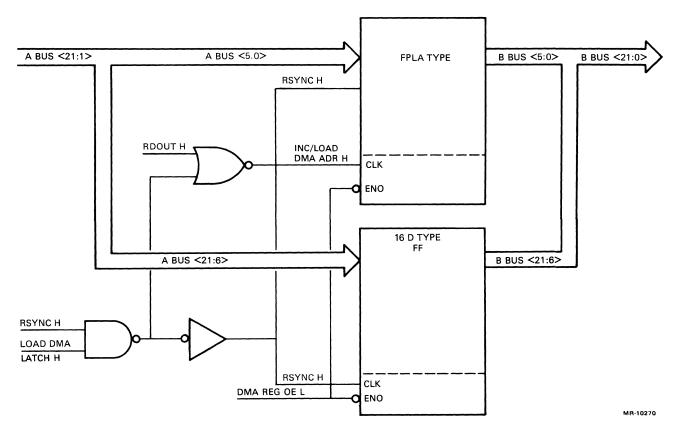

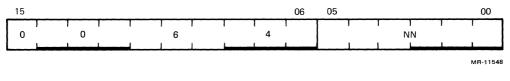

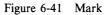

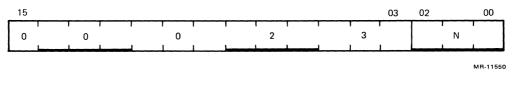

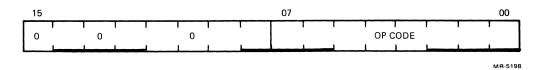

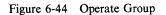

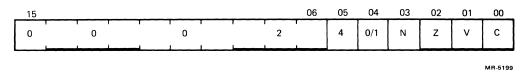

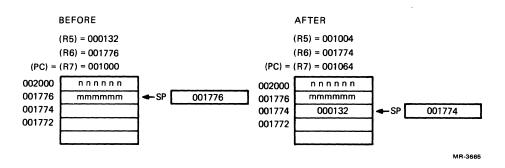

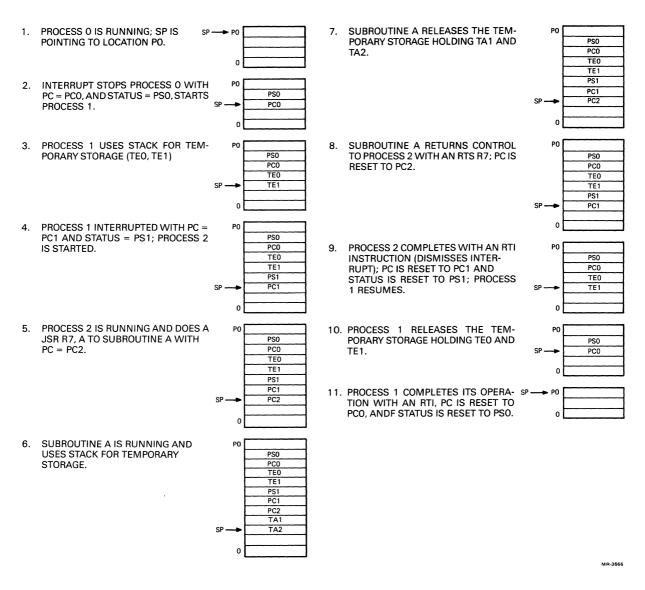

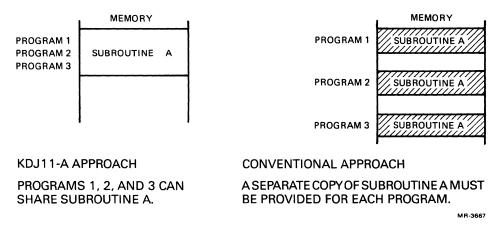

| 4-22       KDJ11-A Bus Transmitters.       4-25         4-23       DCJ11-A Output Control.       4-26         4-24       DCJ11-A Input Control.       4-26         4-25       DMA Monitor Register       4-27         4-26       Initialization/Maintenance Register Logic.       4-28         4-27       Status LEDs Logic       4-29         5-1       DATI Bus Cycle       5-6         5-2       DATI Bus Cycle Timing.       5-6         5-3       DATO or DATO(B) Bus Cycle.       5-10         5-4       DATO or DATO(B) Bus Cycle Timing.       5-9         5-5       DATIO or DATIO(B) Bus Cycle Timing.       5-11         5-6       DATIO or DATIO(B) Bus Cycle Timing.       5-11         5-7       DATBI Bus Cycle Timing.       5-11         5-8       DATBO Bus Cycle Timing.       5-14         5-9       DMTR Bus Cycle Timing.       5-14         5-10       DMA Request/Grant Bus Cycle Timing.       5-15         5-10       DMA Request/Grant Bus Cycle Timing.       5-16         5-11       Interrupt Request/Acknowledge Sequence.       5-18         5-12       Interrupt Request/Cachowledge Sequence.       5-18         5-13       Position-Dependent Configuration.       5-2                                                     |       |                                           |        |